Përmbajtje:

- Hapi 1: Çfarë është Vivado HLS?

- Hapi 2: Biblioteka e videove HLS

- Hapi 3: Sintetizimi

- Hapi 4: Versionimi dhe informacione të tjera për eksport

- Hapi 5: Eksportimi në një Bibliotekë Vivado IP

- Hapi 6: Sinteza dhe Analiza e Eksportit

- Hapi 7: Shtimi i Bibliotekës IP në Vivado

- Hapi 8: Të bësh një azhurnim

- Hapi 9: Të dhëna dhe informacion shtesë

- Hapi 10: Output dhe Input

- Hapi 11: Regjistrohu AXI Ndërfaqja

- Hapi 12: Pragma e rrjedhës së të dhënave

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:28.

- E modifikuara e fundit 2025-01-23 15:10.

A keni dashur ndonjëherë të përpunoni video në kohë reale pa shtuar shumë vonesa ose në një sistem të ngulitur? FPGA -të (Grupet e Portave të Programueshme të Fushave) ndonjëherë përdoren për ta bërë këtë; megjithatë, shkrimi i algoritmeve të përpunimit të videos në gjuhë të specifikimit të harduerit si VHDL ose Verilog është frustruese në rastin më të mirë. Hyni në Vivado HLS, mjeti Xilinx që ju lejon të programoni në një mjedis C ++ dhe të gjeneroni kodin e gjuhës së specifikimit të harduerit prej tij.

Softuerët e kërkuar:

- Vivado HLS

- Vivado

- (Nëse përdorni regjistrat AXI) Vivado SDK

(Opsionale) Shkarkoni shembujt e bërë nga Xilinx këtu:

Shembuj video të Xilinx HLS

Hapi 1: Çfarë është Vivado HLS?

Vivado HLS është një mjet i përdorur për të kthyer kodin si c ++ në struktura harduerike që mund të zbatohen në një FPGA. Ai përfshin një IDE për të bërë këtë zhvillim. Pasi të keni përfunduar zhvillimin tuaj të kodit për HLS, mund të eksportoni IP -në tuaj të gjeneruar në një format për përdorim me Vivado.

Shkarkoni skedarët e bashkangjitur dhe vendosini pranë vendit ku do të krijoni projektin tuaj. (riemërtojini përsëri në "top.cpp" dhe "top.h" nëse kanë një emër të rastësishëm)

Hapi 2: Biblioteka e videove HLS

Biblioteka e videove HLS ka dokumentacion me modele referimi në këtë punim: XAPP1167Një burim tjetër i mirë është faqja Xilinx Wiki në lidhje me të.

Filloni Vivado HLS.

Krijoni një projekt të ri.

Merrni skedarët që keni shkarkuar në hapin e mëparshëm dhe shtojini ato si skedarë burimi. (Shënim: skedarët nuk kopjohen në projekt, por mbesin aty ku janë)

Pastaj përdorni butonin Shfleto për të zgjedhur funksionin e sipërm.

Në faqen tjetër, zgjidhni pjesën Xilinx që po përdorni.

Hapi 3: Sintetizimi

Zgjidhja => Drejtoni C Sintezën => Zgjidhja Aktive

Pas 227.218 sekonda, duhet të bëhet. (Shënim: koha juaj e sintezës aktuale do të ndryshojë bazuar në shumë faktorë)

Hapi 4: Versionimi dhe informacione të tjera për eksport

Numrat e versioneve ndërveprojnë me Vivado për t'ju bërë të jeni në gjendje të azhurnoni IP në një dizajn. Nëse është një ndryshim i vogël i versionit, mund të bëhet në vend ndërsa ndryshimet kryesore të versionit kërkojnë që ju të shtoni manualisht bllokun e ri dhe të hiqni atë të vjetër. Nëse ndërfaqet tuaja nuk kanë ndryshuar dhe përditësimi i versionit është i vogël, përditësimi mund të jetë bëhet plotësisht automatikisht duke shtypur butonin IP të përditësimit. Mund të ekzekutoni "report_ip_status" në tastierën Vivado tcl për të parë statusin e IP -së tuaj.

Vendosni numrat e versionit dhe informacione të tjera në Zgjidhja => Cilësimet e zgjidhjes…

Përndryshe, këto cilësime mund të vendosen gjatë eksportit.

Hapi 5: Eksportimi në një Bibliotekë Vivado IP

Zgjidhja => Eksporto RTL

Nëse nuk i keni vendosur detajet e bibliotekës IP në hapin e mëparshëm, mund ta bëni tani.

Hapi 6: Sinteza dhe Analiza e Eksportit

Në këtë ekran ne mund të shohim statistikat në lidhje me modulin tonë të eksportuar, duke treguar se ai plotëson orën tonë të orës prej 10ns (100MHz) dhe sa nga secili burim që përdor.

Me një kombinim të kësaj, Raportit tonë të Sintezës dhe analizës sonë të të Dhënave, ne mund të shohim se duhen 317338 cikle sahati * periudha e orës 10ns * 14 faza tubacioni = 0.04442732 sekonda. Do të thotë që vonesa totale e shtuar nga përpunimi i imazhit tonë është më pak se një e njëzeta e sekondës (kur matet në 100MHz të synuar).

Hapi 7: Shtimi i Bibliotekës IP në Vivado

Për të përdorur bllokun tuaj të sintetizuar IP, do t'ju duhet ta shtoni atë në Vivado.

Në Vivado shtoni një depo IP në projektin tuaj duke shkuar në katalogun IP dhe klikoni me të djathtën duke zgjedhur "Shto depo …"

Shkoni te drejtoria juaj e projektit Vivado HLS dhe zgjidhni drejtorinë tuaj të zgjidhjeve.

Duhet të raportojë IP -në që ka gjetur.

Hapi 8: Të bësh një azhurnim

Ndonjëherë ju duhet të bëni ndryshime në bllokun tuaj HLS pasi ta përfshini atë në një dizajn Vivado.

Për ta bërë këtë, ju mund të bëni ndryshimet dhe të sintetizoni dhe eksportoni IP me një numër versioni më të lartë (shikoni detajet në hapin e mëparshëm në lidhje me ndryshimet kryesore të numrit të versionit).

Pas ndryshimit të eksportimit të versionit të ri, rifreskoni depot tuaja IP në Vivado. Kjo ose mund të bëhet kur Vivado vëren se IP ka ndryshuar në depo, ose aktivizohet me dorë. (Shënim, nëse rifreskoni depot tuaja IP pas fillimit, por para se të përfundojë eksporti në HLS, IP përkohësisht nuk do të jetë atje, prisni që të përfundojë dhe rifreskoni përsëri.)

Në këtë pikë duhet të shfaqet një dritare me informacionin se një IP është ndryshuar në disk dhe ju jep mundësinë ta përditësoni me një buton "Upgrade Selected". Nëse ndryshimi ishte një ndryshim i vogël i versionit dhe asnjë nga ndërfaqet nuk ndryshoi, atëherë shtypja e atij butoni do të zëvendësojë automatikisht IP -në e vjetër me atë të re, përndryshe mund të kërkohet më shumë punë.

Hapi 9: Të dhëna dhe informacion shtesë

Hapat e mëposhtëm japin më shumë informacion se si funksionon sinteza e HLS dhe çfarë mund të bëni me të.

Për një shembull të një projekti duke përdorur një bllok IP të sintetizuar HLS, shihni këtë udhëzues.

Hapi 10: Output dhe Input

Daljet dhe hyrjet në bllokun përfundimtar IP përcaktohen nga një analizë që sintetizuesi bën për rrjedhën e të dhënave brenda dhe jashtë funksionit të lartë.

Ngjashëm me VHDL ose verilog, HLS ju lejon të specifikoni detaje në lidhje me lidhjet midis IP. Këto rreshta janë shembuj të kësaj:

pavlefshme_filtri i imazhit (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE porti i boshtit = video_në pako = INPUT_STREAM #pragma HLS INTERFACE porti i boshtit = pako video_out = OUTPUT_STREAM #pragma HLS INTERFACE s_axilite port = x pako = CONTROL_BLUSBL

Ju mund të shihni se si portet e ekspozuara në bllokun IP ndikohen nga këto direktiva.

Hapi 11: Regjistrohu AXI Ndërfaqja

Për të marrë hyrje/dalje në/nga blloku juaj IP në PS një mënyrë e mirë për ta bërë këtë është përmes një ndërfaqe AXI.

Ju mund ta specifikoni këtë në kodin tuaj HLS, përfshirë kompensimet që do të përdoren për të hyrë në vlerën më vonë si kjo:

pavlefshme_filtri i imazhit (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite port = x pako = CONTROL_BUS offset = 0x14

#pragma HLS INTERFACE s_axilite port = y pako = CONTROL_BUS offset = 0x1C #pragma HLS flowflow

x = 42;

y = 0xDEADBEEF; }

Pasi të lidheni siç duhet në Vivado, mund të përdorni vlerat duke përdorur këtë kod në Vivado SDK:

#përfshi "parametrat.h"

#përcakto xregoff 0x14 #përcakto yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Kjo do t'ju bëjë që të përfundoni me 42 në x dhe 0xdeadbeef në y

Hapi 12: Pragma e rrjedhës së të dhënave

Brenda #pragma DATAFLOW mënyra se si zbatohet kodi ndryshon nga C ++ normale. Kodi transmetohet në mënyrë që të gjitha udhëzimet të funksionojnë në çdo kohë në pjesë të ndryshme të të dhënave (Mendoni si një linjë montimi në një fabrikë, secili stacion po punon vazhdimisht duke bërë një funksion dhe duke e kaluar atë në stacionin tjetër)

nga imazhi mund të shihni se secila nga direktivat

Pavarësisht se duken si ndryshore normale, objektet img në të vërtetë zbatohen si tamponë të vegjël midis komandave. Përdorimi i një imazhi si hyrje në një funksion e "konsumon" atë dhe e bën atë të papërdorshëm. (Prandaj nevoja për komanda të kopjuara)

Recommended:

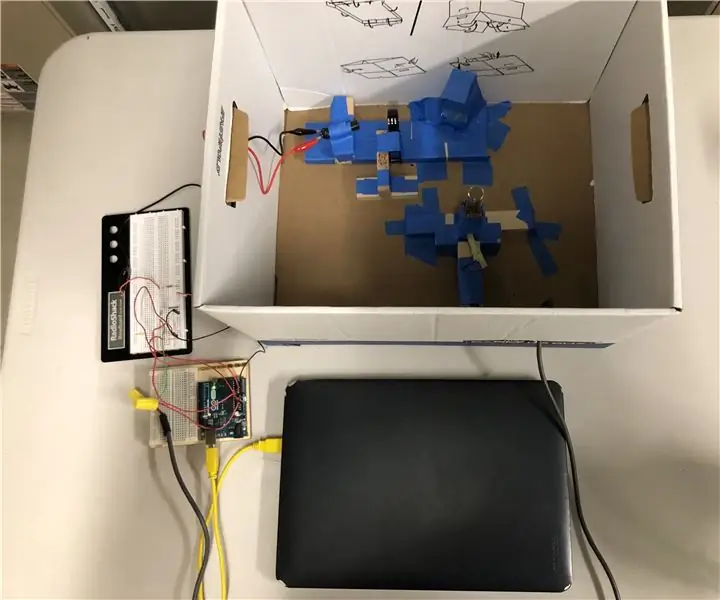

Spektrofotometri i bllokut shtëpiak Jenga për eksperimentet e algave: 15 hapa

Spektrofotometri i Bllokut Jenga i bërë në shtëpi për Eksperimentet e Algave: Algat janë protistë fotosintetikë dhe, si të tillë, janë organizma kritikë në zinxhirët ushqimorë ujorë. Gjatë muajve të pranverës dhe verës, megjithatë, këto dhe mikroorganizma të tjerë mund të shumohen dhe të mposhtin burimet natyrore të ujit, duke rezultuar në pakësimin e oksigjenit

Sinteza Retro e të folurit. Pjesa: 12 IoT, Automatizimi në shtëpi: 12 hapa (me fotografi)

Sinteza Retro e të folurit. Pjesa: 12 IoT, Automatizimi i Shtëpisë: Ky artikull është i 12 -ti në një seri mbi Automatizimin e Shtëpisë Udhëzues që dokumentojnë mënyrën e krijimit dhe integrimit të një Pajisjeje Sinteze të Retro Fjalimit IoT në një sistem ekzistues të automatizimit të shtëpisë duke përfshirë të gjithë funksionalitetin e nevojshëm të softuerit për të mundësuar

Si të përdorni Simulimin Vivado: 6 hapa

Si të përdorni Simulimin Vivado: Unë e kam bërë këtë projekt simulimi për një klasë në internet. Projekti është shkruar nga Verilog. Ne do të përdorim simulimin në Vivado për të vizualizuar formën e valës në enable_sr (aktivizo shifrën) nga projekti stop watch i krijuar më parë. Përveç kësaj, ne do të

Sinteza analoge e zërit në kompjuterin tuaj: 10 hapa (me fotografi)

Sinteza analoge e zërit në kompjuterin tuaj: Ashtu si tingulli i atyre sintetizatorëve të vjetër analogë? Dëshironi të luani me një në kohën tuaj, në vendin tuaj, për aq kohë sa dëshironi, FALAS? Këtu janë realizuar ëndrrat tuaja më të egra Moog. Ju mund të bëheni një artist regjistrues elektronik ose jus

Çmontoni një transformator të bllokut E: 6 hapa

Çmontoni një E-block Transformer: Kam planifikuar të bëj një kamionçinë me kitarë, por më mungonte tela e emaluar. Me qëllim që të përpiqesha ta bëja pa blerë asgjë, mendova për një kohë dhe më erdhi ideja për ta nxjerrë nga një transformator për rrotulluesin tim të vjetër të antenës. Për fat të keq, g