Përmbajtje:

- Hapi 1: Shtoni burime dhe zgjidhni "Shto ose Krijo Burime Simulimi

- Hapi 2: Krijoni një skedar të quajtur Enable_sr_tb

- Hapi 3: Krijoni Skedarin Testbench

- Hapi 4: Vendoseni Enable_sr_tb si nivelin më të lartë nën Simulim

- Hapi 5: Drejtoni Sintezën dhe Simulimin e Sjelljes

- Hapi 6: Vlerësoni rezultatin e Simulimit

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:25.

- E modifikuara e fundit 2025-01-23 15:10.

Unë e kam bërë këtë projekt simulimi për një klasë në internet. Projekti është shkruar nga Verilog. Ne do të përdorim simulimin në Vivado për të vizualizuar formën e valës në enable_sr (aktivizo shifrën) nga projekti stop watch i krijuar më parë. Përveç kësaj, ne do të përdorim detyrën e sistemit për të shfaqur gabimin e bërë nga ne në dizajn.

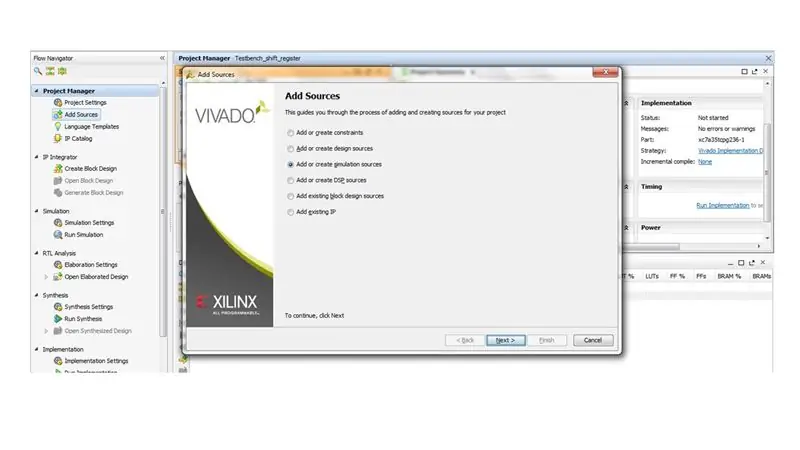

Hapi 1: Shtoni burime dhe zgjidhni "Shto ose Krijo Burime Simulimi

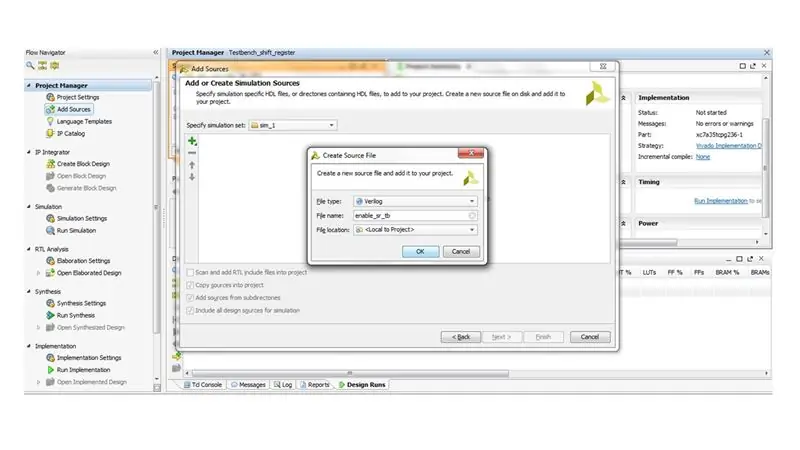

Hapi 2: Krijoni një skedar të quajtur Enable_sr_tb

Hapi 3: Krijoni Skedarin Testbench

1. Importoni modulin enable_sr nga projekti stop watch. Ky është skedari që duam të simulojmë

2. Krijo modul testbench enable_sr_tb ();

3. Shkruani hyrjet dhe daljet e modulit enable_sr (). Mbani mend që hyrjet për enable_sr tani janë në llojin e regjistrit ndërsa daljet bëhen tip neto.

4. Instaloni njësinë nën provë (uut) e cila është enable_sr

5. Gjeneroni orën cila periudhë (T) është 20ns

6. Përdorni deklaratën e kushtëzuar për të krijuar një sistem të kontrollimit të gabimeve. Në këtë shembull, ne duam të kontrollojmë nëse ka më shumë se një shifër aktive.

Shënim: Në skedarin origjinal enable_sr (), duhet të inicojmë modelin si 4’b0011 në mënyrë që të ketë dy shifra që janë aktivë për të krijuar gabim

7. Përdorni detyrën e sistemit $ display për të treguar gabimin

8. Përdorni detyrën e sistemit $ finish për të përfunduar simulimin në kohën 400ns

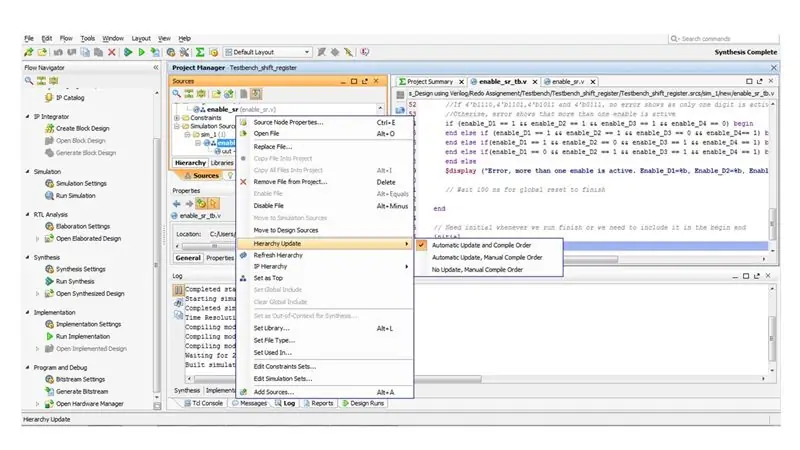

Hapi 4: Vendoseni Enable_sr_tb si nivelin më të lartë nën Simulim

Hapi 5: Drejtoni Sintezën dhe Simulimin e Sjelljes

- Para se të ekzekutoni simulimin e sjelljes, ekzekutoni sintezën për t'u siguruar që nuk ka ndonjë gabim sintaksor në skedarin dhe njësinë testbench nën skedarin e testimit

- Drejtoni simulimin e sjelljes

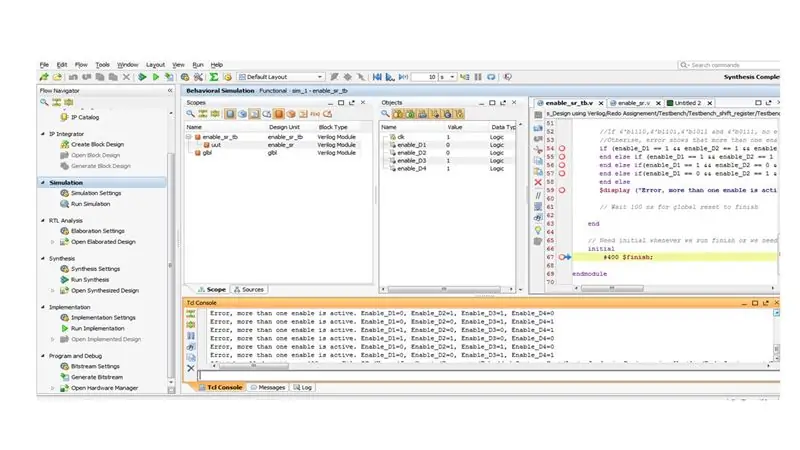

Hapi 6: Vlerësoni rezultatin e Simulimit

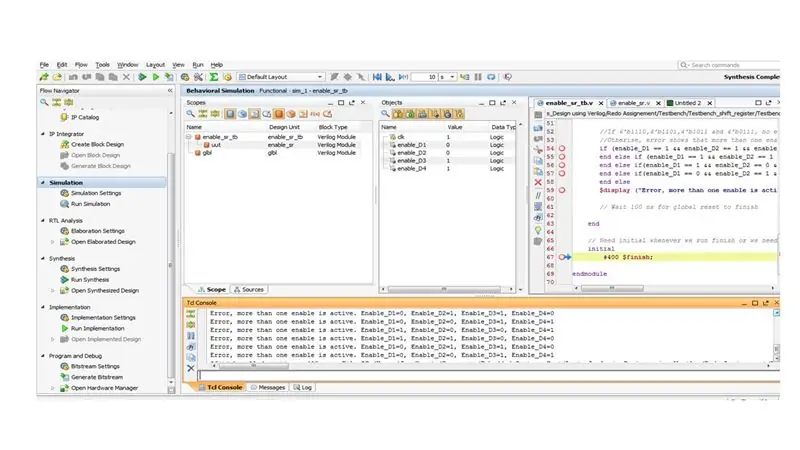

Do të shihni dritaret e simulimit. Ai përmban panele të ndryshme.

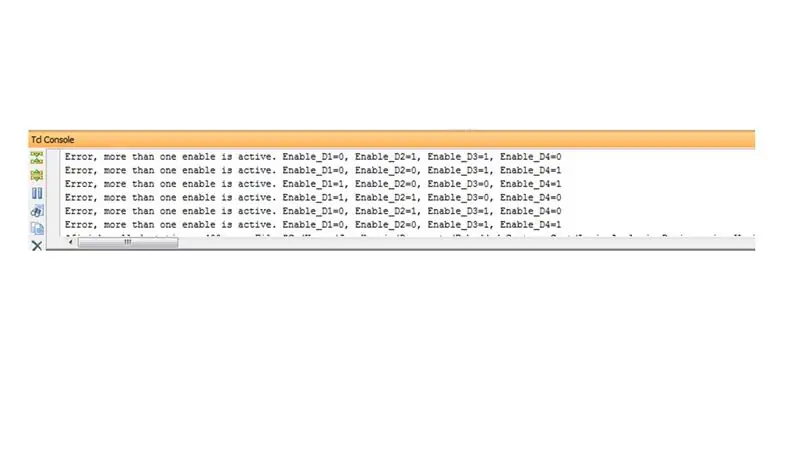

Do të shihni mesazhin e gabimit në panelin e tastierës. Kjo tregon se më shumë se një shifër janë aktive gjatë periudhës së simulimit.

Ju gjithashtu mund të shihni formën e valës në fushën

Bashkangjitur është skedari i projektit.

Recommended:

Visuino Si të përdorni modulimin e gjerësisë së pulsit (PWM) për të ndryshuar shkëlqimin e një LED: 7 hapa

Visuino Si të përdorni modulimin e gjerësisë së pulsit (PWM) për të ndryshuar shkëlqimin e një LED: Në këtë tutorial ne do të përdorim një LED të lidhur me Arduino UNO dhe Visuino për të bërë një ndryshim në shkëlqimin e tij duke përdorur modulimin e gjerësisë së pulsit (PWM). Shikoni një video demonstruese

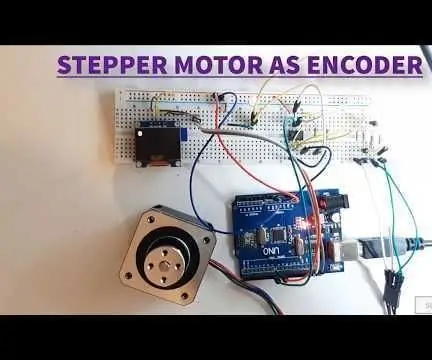

Si të përdorni Stepper Motor si kodues rrotullues dhe ekran OLED për hapa: 6 hapa

Si të përdorni Stepper Motor si kodues rrotullues dhe ekran OLED për hapa: Në këtë tutorial ne do të mësojmë se si të gjurmojmë hapat e motorit stepper në ekranin OLED. Shikoni një video demonstruese. Kredia për tutorialin origjinal shkon për përdoruesit e youtube " sky4fly "

Si të përdorni terminalin Mac dhe si të përdorni funksionet kryesore: 4 hapa

Si të përdorni terminalin Mac dhe si të përdorni funksionet kryesore: Ne do t'ju tregojmë se si të hapni terminalin MAC. Ne gjithashtu do t'ju tregojmë disa veçori brenda Terminalit, të tilla si ifconfig, ndryshimi i drejtorive, qasja në skedarë dhe arp. Ifconfig do t'ju lejojë të kontrolloni adresën tuaj IP dhe reklamën tuaj MAC

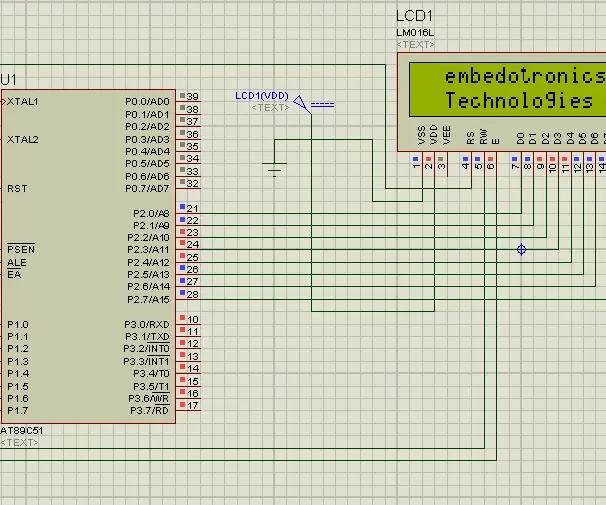

Ndërfaqja e mikrokontrollorit 8051 me 16*2 LCD në Simulimin Proteus: 5 hapa (me fotografi)

Ndërfaqja e Mikrokontrolluesit 8051 Me 16*2 Lcd në Simulimin Proteus: Ky është një projekt shumë themelor i 8051. Në këtë projekt ne do t'ju tregojmë se si mund të ndërlidhim mikrokontrolluesin 16*2 LCD me 8051. Pra, këtu ne po përdorim modalitetin e plotë 8 bit. Në tutorialin tjetër do të tregojmë edhe për modalitetin 4 bit

Sinteza e Bllokut IP të Vivado HLS Video: 12 Hapa

Sinteza e Bllokut IP të Vivado HLS Video: A keni dashur ndonjëherë të përpunoni video në kohë reale pa shtuar shumë vonesa ose në një sistem të ngulitur? FPGA -të (Grupet e Portave të Programueshme të Fushave) ndonjëherë përdoren për ta bërë këtë; megjithatë, shkrimi i algoritmeve të përpunimit të videos në specifikimet e harduerit