Përmbajtje:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:17.

- E modifikuara e fundit 2025-01-23 15:10.

Unë jam i tronditur nga lloji i përgjigjeve që marr në këtë blog. Faleminderit djema që vizituat blogun tim dhe më motivuat të ndaja njohuritë e mia me ju. Këtë herë, unë do të paraqes modelin e një moduli tjetër interesant që shohim në të gjitha SOC - Kontrolluesi i Ndërprerjes.

Ne do të krijojmë një kontrollues të thjeshtë por të fuqishëm të programueshëm të ndërprerjeve. Shtë një dizajn plotësisht i konfigurueshëm dhe i parametruar i cili është i lëvizshëm nëpër platforma. Unë e kam projektuar këtë pasi kam lexuar shumë për disa arkitektura të njohura të kontrolluesve të ndërprerjeve atje si NVIC, 8259a, RISC-V PLIC, Microblaze's INTC, etj. Shpresoj se juve ju duket ky blog i dobishëm dhe ju ndihmon të merrni një shije sesi trajtohen ndërprerjet nga një procesor me ndihmën e një kontrolluesi ndërprerjeje.

Hapi 1: Specifikimet

Më poshtë janë specifikimet e IP:

- Ndërfaqja AHB3-Lite.

-

Parametrat e konfigurueshëm statistikisht:

- Nr. I burimeve të jashtme të ndërprerjes; mbështet deri në 63 ndërprerje.

- Nr. I niveleve prioritare; mbështet deri në 63 nivele.

- Nr. I niveleve të foleve; mbështet deri në 8 nivele fole.

- Gjerësia e autobusit; 32 ose 64.

- Ndërprerjet e maskueshme në nivel global dhe lokal.

- Niveli prioritar i konfigurueshëm në mënyrë dinamike për çdo ndërprerje.

- Dy mënyra të funksionimit - Modaliteti i Fletuar plotësisht dhe Mënyra e Prioritetit të Barabartë.

- Mbështet ndërprerjet e ndjeshme të nivelit aktiv të lartë.

Specifikimet e RISC-V PLIC të frymëzuara mekanizmi i ndërprerjes së shtrëngimit të dorës përdoret në dizajn.

Parablerja e ndërprerjes është frymëzuar nga 8259a

Lexime të tjera: Microblaze INTC, NVIC

Hapi 2: Pasqyrë e PIC

Kontrolluesi i Programueshëm i Ndërprerjeve (PIC) merr ndërprerje të shumta nga pajisjet periferike të jashtme dhe i bashkon ato në një dalje të vetme ndërprerjeje në një bërthamë të synuar të procesorit.

PIC kontrollohet përmes regjistrave të kontrollit dhe statusit. Të gjithë regjistrat PIC janë të hartuar në memorie dhe aksesohen përmes ndërfaqes së autobusit AHB3-Lite.

Banka e regjistrit përbëhet nga regjistri i konfigurimit, regjistrat e mundshëm, regjistrat në pritje, regjistrat në shërbim, regjistrat me përparësi dhe regjistri i ID, të cilat janë tipike në Kontrolluesit e Ndërprerjeve.

Regjistri i konfigurimit përdoret për të vendosur mënyrën e funksionimit të PIC. Mund të funksionojë ose në Modalitetin Fletësisht të Futur ose në Modalitetin e Prioritetit të Barabartë.

Çdo ndërprerje mund të caktohet me përparësi dhe të maskohet individualisht. Maskimi global i të gjitha ndërprerjeve gjithashtu mbështetet.

Banka e regjistrit ndërvepron me Priority Resolver dhe BTC (Binary-Tree-Comparator) për të zgjidhur përparësitë e ndërprerjeve në pritje dhe për të pohuar ndërprerjen në përpunim në përputhje me rrethanat. Regjistri i ID -së përmban ID -në e ndërprerjes me përparësi më të lartë në pritje.

Hapi 3: Dizajni dhe Zbatimi i RTL

Struktura e dizajnit të PIC në zvogëlimin e vonesës së zgjidhjes së prioriteteve, e cila është pjesa më kritike në kohë e projektimit. Meqenëse dizajni zgjidh përparësitë në një cikël të vetëm të orës, performanca degradon me rritjen e numrit të burimeve me një kompleksitet Log2.

Dizajni u zbatua me sukses dhe koha u verifikua deri në frekuencat e mëposhtme në Artix-7 FPGA.

- Deri në 15 burime: 100 MHz

- Deri në 63 burime: 50 MHz

Vonesa e ndërprerjes e shtuar vetëm nga PIC është 3 cikle sahati (Duke përjashtuar kohën e ndërrimit të kontekstit të Procesorit dhe kohën e parë të marrjes së udhëzimit ISR).

Hapi 4: Shënime të rëndësishme dhe skedarë të bashkangjitur

Shënime të rëndësishme:

- Nëse ndërfaqja AHB3-Lite është e padëshirueshme, mund të ndryshoni modulin e sipërm dhe të përdorni modelin e skeletit të PIC. Sidoqoftë, paneli i provës i dhënë është për IP me ndërfaqe AHB3-Lite.

- PIC IP v1.0 është një dizajn plotësisht portativ, i zhveshur RTL.

- Verifikuar funksionalisht për të punuar në të dyja mënyrat.

Skedarët e bashkangjitur:

- Kodet e projektimit dhe tryezës në VHDL.

- Dokumentacioni i plotë IP.

Shtë një dizajn me burim të hapur… Mos ngurroni të përdorni…

Për çdo pyetje, në çdo kohë:

Mitu Raj

Recommended:

Dizajni i marrjes, përforcimit dhe filtrimit të një qarku të një elektrokardiogrami bazë: 6 hapa

Dizajni i marrjes, përforcimit dhe filtrimit të qarkut të një elektrokardiogrami bazë: Për të përfunduar këtë udhëzues, të vetmet gjëra që nevojiten janë një kompjuter, qasje në internet dhe disa softuerë simulues. Për qëllimet e këtij dizajni, të gjitha qarqet dhe simulimet do të funksionojnë në LTspice XVII. Ky program simulimi përmban

Dizajnimi i një Kontrolluesi të Simuluar të Cache Asociative me Katër Drejtime në VHDL: 4 Hapa

Dizajni i një Kontrolluesi të thjeshtë të Asociuar të Cache me katër drejtime në VHDL: Në udhëzimet e mia të mëparshme, ne pamë se si të krijojmë një kontrollues të thjeshtë të cache të hartuar drejtpërdrejt. Këtë herë, ne bëjmë një hap përpara. Ne do të dizajnojmë një kontrollues të thjeshtë cache të asociuar me katër drejtime. Avantazh? Më pak norma e humbjes, por me koston e performancës

Dizajni i një kontrolluesi të thjeshtë të cache në VHDL: 4 hapa

Dizajni i një Kontrolluesi të Thjeshtë Cache në VHDL: Unë po e shkruaj këtë gjë të udhëzueshme, sepse e pashë pak të vështirë të merrja një kod referimi VHDL për të mësuar dhe filluar hartimin e një kontrolluesi të cache. Kështu që unë krijova një kontrollues të cache vetë nga e para dhe e testova me sukses në FPGA. Kam p

Dizajni i një kontrolluesi të thjeshtë VGA në VHDL dhe Verilog: 5 hapa

Dizajni i një kontrolluesi të thjeshtë VGA në VHDL dhe Verilog: Në këtë udhëzues, ne do të hartojmë një kontrollues të thjeshtë VGA në RTL. Kontrolluesi VGA është qark dixhital i krijuar për të drejtuar ekranet VGA. Lexohet nga Frame Buffer (VGA Memory) i cili përfaqëson kornizën që do të shfaqet, dhe gjeneron nevoja

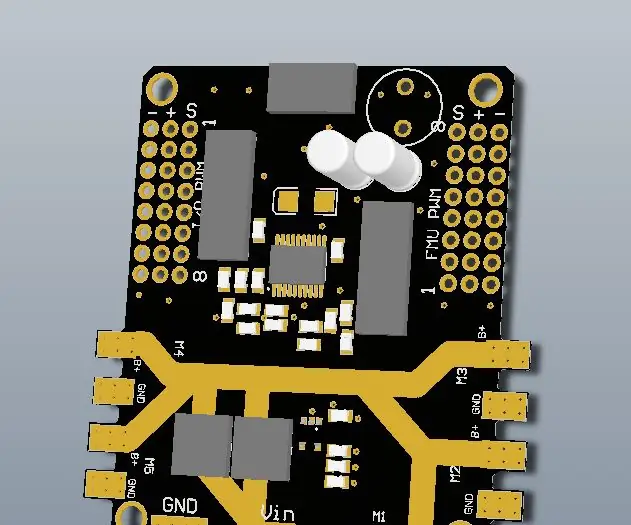

Dizajni i një PDB të Fuqisë së Lartë (Bordi i Shpërndarjes së Energjisë) për një Pixhawk: 5 hapa

Dizajni i një PDB të Fuqisë së Lartë (Bordi i Shpërndarjes së Fuqisë) për një Pixhawk: Një PCB për t'i fuqizuar të gjithë! Aktualisht shumica e materialeve që ju nevojiten për të ndërtuar një dron janë të lira në internet, kështu që ideja për të bërë një PCB të vetë-zhvilluar nuk ia vlen aspak përveç disa rasteve kur doni të bëni një gjë të çuditshme dhe