Përmbajtje:

- Hapi 1: Ndërtimi i një Moduli PWM- Skedari Burimor

- Hapi 2: Ndërtimi i një Moduli PWM- Konfigurimi Vivado

- Hapi 3: Ndërtimi i një moduli PWM- Krijoni një skedar projekti

- Hapi 4: Ndërtimi i një Moduli PWM- Blloku i Dizajnit dhe Vendosja e Kufizimit të Skedarit (I)

- Hapi 5: Ndërtimi i një Moduli PWM- Dizajni i Bllokut dhe Vendosja e Skedarit të Kufizimit (II)

- Hapi 6: Ndërtimi i një moduli PWM- Blloku i dizajnit dhe vendosja e skedarit të kufizimit (III)

- Hapi 7: Ndërtimi i një Moduli PWM- Dizajni i Bllokut dhe Vendosja e Skedarit të Kufizimit (IV)

- Hapi 8: Ndërtimi i një Moduli PWM- Blloku i Dizajnit dhe Vendosja e Kufizimit të Skedarit (V)

- Hapi 9: Ndërtimi i një moduli PWM- Instalimi i harduerit

- Hapi 10: Ndërtimi i një Moduli PWM- Gjeneroni Bitstream dhe Nisni SDK

- Hapi 11: Ndërtimi i një Moduli PWM- Krijoni një Aplikacion të Ri në Xilinx SDK

- Hapi 12: Ndërtimi i një Moduli PWM- Vështrim i Përgjithshëm i Projektit Explorer (I)

- Hapi 13: Ndërtimi i një Moduli PWM- Vështrim i Përgjithshëm i Projektit Explorer (II)

- Hapi 14: Ndërtimi i një Moduli PWM- Vështrim i Përgjithshëm i Projektit Explorer (III)

- Hapi 15: Ndërtimi i një moduli PWM- Përfundoni funksionin PWM (I)

- Hapi 16: Ndërtimi i një moduli PWM- Përfundoni funksionin PWM (II)

- Hapi 17: Ndërtimi i një Moduli PWM- Përfundoni Funksionin PWM (III)

- Hapi 18: Ndërtimi i një moduli PWM- Bëni të funksionojë

- Hapi 19: Transmetimi i përpunimit të videove në Digilent ZYBO Me OV7670

- Hapi 20: Plotësoni Diagramin e Bllokut

- Hapi 21: Lidhni OV7670 me ZYBO

- Hapi 22: Krijoni Dizajn Blloku

- Hapi 23: Shtoni skedarë VHDL për kontrollin dhe kapjen e kamerës OV7670

- Hapi 24: Shtoni Skedarin e Kufizimeve

- Hapi 25: Shtoni IP Repo për HLS IP

- Hapi 26: Shtoni module dhe IP

- Hapi 27: Cilësimet e konfigurimit të IP

- Hapi 28: Shtoni dhe Konfiguroni Bllokun IP të PS

- Hapi 29: Pjesa 1. Ndërtimi i një Moduli PWM për Servo Motors

- Hapi 30: Lidhjet anësore të hyrjes së videos (e theksuar aklk)

- Hapi 31: Lidhjet me OV7670

- Hapi 32: Lidhjet në Video Out Side

- Hapi 33: Drejtoni Automatizimin e Bllokut dhe Lidhjes

- Hapi 34: Gjeneroni mbështjellës HDL

- Hapi 35: Gjeneroni Bitstream, Eksportoni Hardware në SDK, Nisni SDK Nga Vivado

- Hapi 36: SDK (pa FreeRTOS)

- Hapi 37: Zbatimi i FreeRTOS

- Hapi 38: Udhëzimet e përdorimit

- Hapi 39: Referencat dhe Lidhjet

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:28.

- E modifikuara e fundit 2025-01-23 15:10.

Filloni në hapin një për detaje mbi krijimin e një kontrolluesi servo PWM me 2 boshte.

Filloni në bllok skemën masive (Hapi 19) për projektin e plotë.

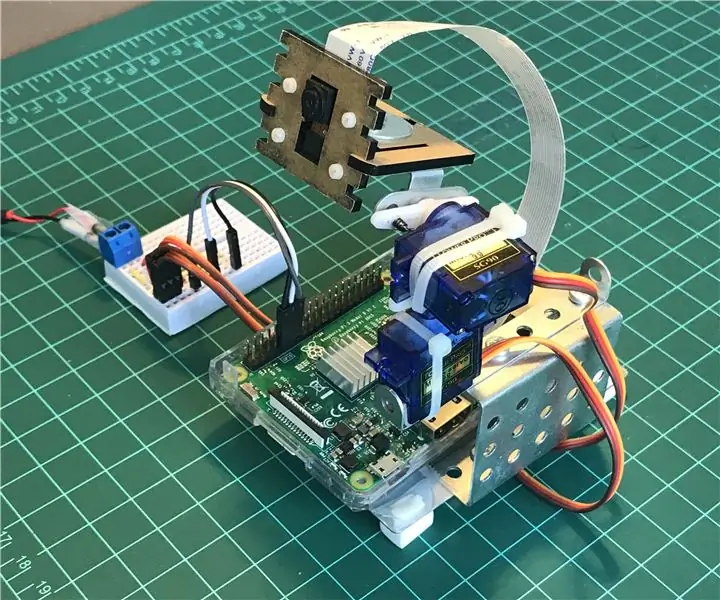

Kamera + Konfigurimi i tiganit/pjerrësisë që përdorëm:

PmodCON3 nga Digilent u përdor për të lidhur servot.

Hapi 1: Ndërtimi i një Moduli PWM- Skedari Burimor

Hapi 2: Ndërtimi i një Moduli PWM- Konfigurimi Vivado

Së pari, shkarkoni uebfaqen e Vivado Design Suite Nga Xilinx. Instaloni të gjithë kompletin e dizajnit, duke përfshirë Vivado Software Development Kit (SDK). Ky projekt përdor versionin 2017.2.

Ndërkohë, Digilent Adept 2 gjithashtu duhet të instalohet si një drejtues bordi Zybo.

Hapi 3: Ndërtimi i një moduli PWM- Krijoni një skedar projekti

Para se të krijoni një skedar projekti, duhet të siguroheni që tashmë e keni instaluar skedarin Zybo siç duhet si udhëzues këtu:

Vivado Version 2015.1 dhe më vonë Instalimi i Skedarit të Bordit

Hap Vivado 2017.2. Në Fillimin e Shpejtë, klikoni në Krijo Projekt -> Tjetër -> Emri i Projektit (Emërtoni emrin e projektit tuaj këtu) -> Lloji i Projektit. Në Llojin e Projektit, zgjidhni RTL Project dhe shënoni në "Mos specifikoni burimet në këtë kohë". Tjetra, për Pjesën e Parazgjedhur, zgjidhni "Bordet" dhe "Zybo" si Emri i Shfaqur. Tjetra, Kliko Finish për të filluar projektin.

Hapi 4: Ndërtimi i një Moduli PWM- Blloku i Dizajnit dhe Vendosja e Kufizimit të Skedarit (I)

Në Flow Navigator, klikoni në "" Krijo dizajn blloku ", pastaj shtypni OK. klikoni shenjën "+" për të shtuar IP -të e nevojshme. Shto:

- Një sistem përpunimi ZYNQ7 Dy kohëmatës AXI

- Dy kohëmatës AXI

Hapi 5: Ndërtimi i një Moduli PWM- Dizajni i Bllokut dhe Vendosja e Skedarit të Kufizimit (II)

Pas Shtimit të IP -ve, Drejtoni Automatizimin e Bllokut dhe automatizimin e lidhjes. Pasi të përfundojë automatizimi, në bllokun "axi_timer_0", kliko me të djathtën në pwm0 -> Make External. Emërtoni pinin e jashtëm pwm0 si pwm_Xaxis. Gjithashtu, përsëritni procesin e mësipërm në bllokun "axi_timer_1" dhe emërtoni pinin e jashtëm pwm0 si pwm_Zaxis.

Hapi 6: Ndërtimi i një moduli PWM- Blloku i dizajnit dhe vendosja e skedarit të kufizimit (III)

Vini re se çdo herë kur të përfundojmë Dizajnin e Bllokut në Vivado, duhet të krijojmë një Mbështjellës HDL. Meqenëse do të jetë moduli i nivelit të lartë për secilin projekt.

Hapi 7: Ndërtimi i një Moduli PWM- Dizajni i Bllokut dhe Vendosja e Skedarit të Kufizimit (IV)

Tani, ne duhet të vendosim skedarin tonë të kufizimit për të caktuar kunjat e lidhur me bllok -diagramin tonë. Mbyllni dritaren e Dizajnit të Bllokut, në skedën "Burimet", "Shto burime"-> Shtoni ose krijoni kufizime-> shtoni Zybo-Master.xdc si skedarët tanë kufizues.

Hapi 8: Ndërtimi i një Moduli PWM- Blloku i Dizajnit dhe Vendosja e Kufizimit të Skedarit (V)

Hapni skedarin e kufizimit Zybo-Master.xdc nga dosja Kufizimet, mos komentoni portet që duam të specifikojmë si sinjale dalëse dhe riemërtoni “get_ports {XXXX}”, i cili XXXX tregon pinin e jashtëm të emërtuar në Diagramin e Bllokut. Vendosja e skedarit të kufizimit është treguar në figurë.

Hapi 9: Ndërtimi i një moduli PWM- Instalimi i harduerit

Lidhni motorët servo me Pmod CON3. TowerPro SG90 është modeli servo motor që kemi përdorur në këtë projekt. Për telat e servo motorit, tela portokalli përfaqëson sinjalin PWM, të lidhur me kunjin SIG në Pmod CON3. Teli i kuq Vcc është një tel i energjisë i lidhur me pin VS në Pmod CON3. Së fundi, tela ngjyrë kafe Gnd është një tel i tokëzuar i lidhur me kunjin GND. Tjetra, futni Pmod CON3 në rreshtin e sipërm të portit JD në Bordin Zybo.

Hapi 10: Ndërtimi i një Moduli PWM- Gjeneroni Bitstream dhe Nisni SDK

1. Në skedën Project Navigator, ekzekutoni Generate BitStream.

2. Eksportoni pajisjet: Skedari> Eksporti> Eksporti i pajisjeve-> shënoni në "përfshini bitstream"-> OK 3. Nisni SDK: Skedar-> Nisni SDK.

Hapi 11: Ndërtimi i një Moduli PWM- Krijoni një Aplikacion të Ri në Xilinx SDK

Krijoni një aplikacion të ri:

Skedar> E Re> Projekti i Aplikimit -> Shkruani emrin e projektit tuaj -> Përfundo

Nën Project Explorer, duhet të ketë tre dosje.

Në këtë rast, "design_1_wrapper_hw_platform_0" është dosja e eksportuar më parë nga Vivado. Axis_2_PWM_SDK_bsp është dosja e paketës së mbështetjes së bordit. Dhe Axis_2_PWM_SDK është dosja jonë kryesore e projektit në SDK. Ju mund të shihni skedarin "helloworld.c" nën dosjen "src" të Axis_2_PWM_SDK, ku "helloworld.c" është skedari kryesor.

Hapi 12: Ndërtimi i një Moduli PWM- Vështrim i Përgjithshëm i Projektit Explorer (I)

Le të kontrollojmë disa skedarë nën Project Explorer. Së pari, në dosjen "design_1_wrapper_hw_platform_0", hapni "system.hdf". Ky skedar demonstron hartën e adresave për procesorin ps7_cortex9 dhe blloqet IP të pranishme në dizajnin tonë.

Hapi 13: Ndërtimi i një Moduli PWM- Vështrim i Përgjithshëm i Projektit Explorer (II)

Pastaj, kontrolloni skedarin "përfshi" dhe "libsrc" nën dosjen "Axis_2_PWM_SDK_bsp". Skedarët e bibliotekës këtu na mundësojnë të ndërveprojmë me pajisjet periferike pa regjistra "duke luajtur".

Hapi 14: Ndërtimi i një Moduli PWM- Vështrim i Përgjithshëm i Projektit Explorer (III)

Përmes dokumentacionit BSP, xtmrctr.h gjendet si Biblioteka e Kontrollit të Kohëmatësit Xilinx që lidhet me AXI Timer. Në mënyrë tipike, ne mund të gjejmë funksionin e dëshiruar PWM këtu. Sidoqoftë, nëse lexoni dokumentacionin "tmrctr_v4_3", kjo tregon se shoferi aktualisht nuk e mbështet funksionimin PWM të pajisjes. Për shkak të mangësisë në funksionin PWM, ne duhet të mbyllim funksionin tonë PWM me ndihmën e xtmrctr.h dhe AXI Timer v2.0 LogiCORE IP Guide Product.

Hapi 15: Ndërtimi i një moduli PWM- Përfundoni funksionin PWM (I)

Kthehuni te skedari kryesor "helloworld.c", përfshini skedarët e mëposhtëm të kokës:

Hapi 16: Ndërtimi i një moduli PWM- Përfundoni funksionin PWM (II)

Përcaktoni adresat bazë të dy AXI TImer përmes "xparameters.h".

Hapi 17: Ndërtimi i një Moduli PWM- Përfundoni Funksionin PWM (III)

Ndërtoni funksionin e dëshiruar PWM.

Duty_val: konverton vlerën e shkallës në ciklin e punës. PWM_Freq_Duty: vendosni frekuencën e dëshiruar dhe ciklin e punës për të gjeneruar PWM. Periudha e orës gjithashtu duhet të caktohet.

PWM_START: caktoni adresën e regjistrit PWM dhe filloni të gjeneroni PWM.

PWM_STOP: caktoni adresën e regjistrit PWM dhe ndaloni së gjeneruari PWM.

Pjesa tjetër e kodit demo tregohet në "helloworld.c" nën "Axis_2_PWM_SDK"

Hapi 18: Ndërtimi i një moduli PWM- Bëni të funksionojë

1. Programoni FPGA përmes SDK

- Lidhni Zybo Board përmes portit USB me PC.

- Mjetet Xilinx -> Programi FPGA

2. Drejtoni programin

Klikoni në ikonën "Run" dhe lëshoni menunë -> Run As -> Launch on Hardware

3. Terminali i SDK -së

- Hapni Terminalin SDK -> Lidhu me Portin Serial -> OK

- Drejtoni programin. Nëse kodi demo funksionon me sukses, duhet të shihni "Fillimi është bërë!" në Terminalin e SDK -së.

Hapi 19: Transmetimi i përpunimit të videove në Digilent ZYBO Me OV7670

Skedari i plotë i arkivit është bashkangjitur.

Hapi 20: Plotësoni Diagramin e Bllokut

Kjo tregon diagramin e plotë të të gjitha lidhjeve dhe blloqeve IP në projekt

Hapi 21: Lidhni OV7670 me ZYBO

Krijoni një lidhje për të lidhur modulin ov7670 me ZYBO Pmods

Të dhënat Pmod janë Pmod D

Kontrolli Pmod është Pmod C

Për më tepër, lidhni PmodCON3 dhe servos siç specifikohet në gjysmën e parë të këtij mësimi

Hapi 22: Krijoni Dizajn Blloku

Në Flow Navigator, klikoni në "Krijo dizajn blloku", pastaj shtypni OK.

Hapi 23: Shtoni skedarë VHDL për kontrollin dhe kapjen e kamerës OV7670

Shtoni skedarët VHDL të bashkangjitur në këtë hap në projekt

Hapi 24: Shtoni Skedarin e Kufizimeve

Shtoni skedarin e bashkëngjitur të kufizimeve në projektin tuaj.

Hapi 25: Shtoni IP Repo për HLS IP

Merrni skedarin Zip të bashkangjitur dhe hapeni atë në një dosje të re të quajtur në mënyrë të ngjashme në një drejtori (dosje) të re të quajtur "HLS_repo".

Shtoni një depo IP në projektin tuaj duke shkuar në katalogun IP dhe klikoni me të djathtën duke zgjedhur "Shto depo …"

Shkoni te drejtoria juaj "HLS_repo" dhe zgjidhni atë.

Opsionale: Krijoni bllokun e përpunimit të videos HLS për veten tuaj!

Hapi 26: Shtoni module dhe IP

Shtoni modulet ov7670_axi_stream_capture, debounce dhe ov7670_controller në bllok diagram duke klikuar me të djathtën në sfond dhe duke zgjedhur "Shto modul …"

Në mënyrë të ngjashme, shtoni IP -të:

- HLS_Video_Track

- Tampon i Kornizës Video Shkruani

- Tampon i kornizës së videos të lexuar

- Kontrolluesi i kohës së videos

- AXI4-Transmeto në Video Out

- 3 të "Fetë"

- Konstante

- 2 të Kohëmatësit AXI

Hapi 27: Cilësimet e konfigurimit të IP

Siç tregohet në fotografi

Hapi 28: Shtoni dhe Konfiguroni Bllokun IP të PS

Shtoni sistemin e përpunimit ZYNQ7 në bllok diagram

modifikoni konfigurimin:

-

Konfigurimi PS-PL

-

HP

- Aktivizo S HP 0

- Aktivizo S HP 1

-

-

Konfigurimi i orës

-

Orë pëlhure PL

- FCLK_0 në 100MHz

- FCLK_1 në 25MHz (OutputClock)

- FLCK_2 në 35MHz (<= 50MHz) (CameraClock)

-

Hapi 29: Pjesa 1. Ndërtimi i një Moduli PWM për Servo Motors

Sillni axi_timer_0 pwm0 në portin e ri të daljes pwm_Xaxis

Sillni axi_timer_1 pwm0 në portin e ri të daljes pwm_Zaxis

Hapi 30: Lidhjet anësore të hyrjes së videos (e theksuar aklk)

Lidhni blloqet IP të anës së hyrjes së videos në mënyrë korrekte

(* këto lidhje duhet të krijohen duke zgjedhur opsionet e duhura gjatë automatizimit të lidhjes) "aclk" nga aksi_stream_capture shkon në:

- ap_clk në tampon të kornizës së videos shkruaj

- ap_clk në bllokun e përpunimit të rrjedhës video HLS

- *aklk në AXI smartconnect IP nga Buffer Video Frame Shkruani në S_AXI_HP0

- *aclk që korrespondon me kanalet e IP -së AXI Interconnect për kanalet S_AXI të bllokut të përpunimit të videos HLS dhe tamponit të kornizës video shkruani S_AXI_HP0_ACLK në bllokun PS

Sinjali i transmetimit video lidhet thjesht në seri nga blloku i kapjes në ndërfaqen e kujtesës Zynq.

- Video kalon nga blloku i kapjes në bllokun e përpunimit HLS.

- Videoja e përpunuar nga blloku HLS shkon në bllokun e shkrimit të tamponit të kornizës.

- *Blloku i shkrimit tampon i kornizës lidhet me ndërfaqen HP0 në bllokun Zynq PS.

- Sinjali m_axis_tuser nga dalja e bllokut të kapjes lidhet me dorë si në sinjalin e hyrjes video_in_TUSER në bllokun e përpunimit HLS ashtu edhe në sinjalin ap_start në të njëjtin bllok.

Sinjali TUSER (tuser) përdoret nga protokolli i transmetimit video AXI për të treguar fillimin e një kornize të videos. AP_Start i thotë bllokut HLS të fillojë përpunimin. Ne po përdorim kështu tuser për të shkaktuar bllokun HLS për të përpunuar çdo kornizë ashtu siç është hyn. Kur lidhni një sinjal të vetëm të një autobusi dhe e ndani atë në këtë mënyrë, është e nevojshme ta lidhni atë gjithashtu me pikën normale të përfundimit të pjesës tjetër të autobusit. Vivado supozon se nëse e lidhni sinjalin me dorë që dëshironi të shkëputni atë me të cilën normalisht do të lidhej.

Cilësimet e konfigurimit të blloqeve IP:

Tamponi i kornizës së videos shkruani:

Formatet e videos: RGB8

1 mostër për orë Kolona maksimale: 1280 (> = 640) Rreshta maksimale: 960 (> = 480) Gjerësia maksimale e të dhënave: 8

Hapi 31: Lidhjet me OV7670

Në bllokun ov7670_axi_stream_capture

- Bëni të gjitha hyrjet të jashtme (klikoni me të djathtën në një kunj dhe zgjidhni nga menyja, ose klikoni me të majtën-> ctrl+T)

- Lërini emrat ashtu siç janë

Në bllokun ov7670_controller

- Bëni të gjitha daljet e bllokut të jashtme

- Riemërtoni portën config_finished në led0

- lidhni clk me CameraClock (<= 50MHz) (FCLK_2)

Në bllokun e debunimit

- lidhni hyrjen e butonit1 me një portë hyrëse të jashtme të quajtur btn0

- lidhni out1 me linjën e ri -dërgimit në bllokun IP të ov7670_controller

- lidhni hyrjen e butonit2 me një portë hyrëse të jashtme të quajtur btn3

- lidhni out2n me hyrjen ext_reset_in në IP të Rivendosjes së Sistemit të Procesorit për domenin e orës së kapjes së videos. (*Kjo mund të ketë nevojë të bëhet pasi të krijohet IP*)

- lidhni clk me CameraClock (<= 50MHz) (FCLK_2)

Hapi 32: Lidhjet në Video Out Side

Lidhjet për blloqet e kontrollit të kohës së videos (VTC), AXI4-Stream to Video Out dhe feta

- Përdorni orën 25MHz (FCLK_1) për vid_io_out_clk dhe VTC clk

- Përdorni orën 100MHz (FCLK_0) për aclk në AXI4-Stream to Video Out

- vtiming_out në vtiming_in

- Tampon i kornizës së videos Lexo m_axis_video shkon në AXI4-Stream to Video Out video_in

- vtg_ce shkon në gen_clken

- Lidheni VTC clken, aclken, vid_io_out_ce me Constant dout [0: 0]

- Sillni vid_hsync dhe vid_vsync në portat e jashtme të daljes vga_hs dhe vga_vs, respektivisht. (jo ne foto)

Feta:

- Feta duhet të vendosen siç tregohet në fotot e bashkangjitura

- riemërtoni blloqet në slice_red, slice_green, dhe slice_blue

- vargjet e konfigurimit të konfigurimit siç tregohen në imazhe sipas emrit të bllokut

- lidhni secilën dalje të fetë me një dalje të portit të jashtëm siç tregohet në imazh.

- vid_data [23: 0] lidhet me hyrjet për secilën fetë (Din [23: 0])

Hapi 33: Drejtoni Automatizimin e Bllokut dhe Lidhjes

Drejtoni Automatizimin e Bllokut për të lidhur gjërat nga blloku PS ZYNQ7. Siç tregohet në foto.

Drejtoni automatizimin e lidhjes për të krijuar të gjithë IP -në e ndërlidhjes. Kushtojini vëmendje të gjitha opsioneve në secilën fotografi.

Në bllokun e daljes, lidheni out2n me domenin e orës së kapjes së videos Procesori i Sistemit Reset ext_reset_in në hyrje.

Hapi 34: Gjeneroni mbështjellës HDL

Krijoni mbështjellësin HDL për modelin tuaj të bllokut.

Vendoseni atë si modulin kryesor.

Hapi 35: Gjeneroni Bitstream, Eksportoni Hardware në SDK, Nisni SDK Nga Vivado

Sigurohuni që të përfshini bitstream në eksport.

Gjenerimi i bitstream mund të marrë një kohë shumë të gjatë.

Pastaj nisni SDK

Hapi 36: SDK (pa FreeRTOS)

Ky version bën gjithçka pa përdorur FreeRTOS, duke e kondensuar bukur kodin.

Krijoni një BSP të pavarur bazuar në modelin e harduerit. Opsionet e paracaktuara duhet të jenë të mira. Sigurohuni që burimet e BSP të jenë krijuar.

Krijoni aplikacion siç tregohet në figurë. (aplikacion bosh)

Fshini autogjenerimin kryesor dhe importoni skedarët e bashkangjitur.

Hapi 37: Zbatimi i FreeRTOS

Ky version përdor FreeRTOS. Krijoni një BSP FreeRTOS901 bazuar në modelin e harduerit. Opsionet e paracaktuara duhet të jenë të mira. Sigurohuni që burimet e BSP të jenë krijuar.

Krijoni aplikacion siç tregohet në figurë. (aplikacion bosh)

Fshini autogjenerimin kryesor dhe importoni skedarët e bashkangjitur.

Hapi 38: Udhëzimet e përdorimit

Ky projekt është pak i ndërlikuar për tu zbatuar. Ndiqni hapat me radhë.

Sigurohuni që ZYBO juaj të mos ngarkojë asgjë kur të ndizet. Kjo do të thotë që LED i Bërë nuk duhet të ndizet. Një mënyrë për ta bërë këtë është të vendosni kërcyesin e burimit të nisjes në JTAG.

Hapni projektin (FreeRTOS ose jo) që dëshironi të programoni nga SDK

- Ndizni ZYBO -në tuaj. LED i Bërë nuk duhet të ndizet.

- Programoni FPGA me skedarin bit. LED i Bërë duhet të ndizet. Led0 nuk duhet të ndizet.

- Drejtoni kodin (mos harroni të kaloni pikën e fillimit nëse e bëni këtë).

Në këtë pikë ju duhet të merrni një dalje në ekranin tuaj VGA.

Për të rinisur (nëse ka defekte ose çfarëdo): trokitni shpejt butonin PS-SRST ose fikni ZYBO dhe pastaj ndizeni përsëri. Vazhdoni nga hapi 2.

Ndalimi i procesorit me korrigjuesin do të bëjë që Kamera të mbajë pozicionin në vend që të lëvizë. Transmetimi i videos do të vazhdojë gjithsesi.

Hapi 39: Referencat dhe Lidhjet

Udhëzuesit dhe dokumentacioni referues i Xilinx:

- PG044 - Transmetimi AXI në Video

- PG278 - Tampon i Kornizës Video Lexoni/Shkruani

Lidhje të tjera:

- Blogu i Laurit - hyrja VDMA

- Blogu i Laurit - OV7670 në daljen VGA duke përdorur BRAM

- Wiki Hamsterworks, nga Mike Fields, burimi origjinal i kodit OV7670

- Fleta e të dhënave që tregon specifikimet bazë të kohës

Recommended:

WIDI - HDMI pa tela duke përdorur Zybo (Bordi i Zhvillimit Zynq): 9 hapa (me fotografi)

WIDI - HDMI pa tel duke përdorur Zybo (Bordi i Zhvillimit Zynq): A keni dëshiruar ndonjëherë që të mund ta lidhni televizorin tuaj me një kompjuter ose laptop si një monitor të jashtëm, por nuk dëshironi të keni të gjitha ato kabllo bezdisëse? Nëse është kështu, ky tutorial është vetëm për ju! Ndërsa ka disa produkte që arrijnë këtë qëllim, një

Mekanizmi Pan dhe Tilt për Kohëzgjatjet DSLR: 7 hapa (me fotografi)

Mekanizmi Pan dhe Tilt për DSLR Time Lapses: Unë kisha disa motorë stepper të shtrirë përreth dhe me të vërtetë doja t'i përdorja ato për të bërë diçka të lezetshme. Vendosa që do të bëja një sistem Pan dhe Tilt për kamerën time DSLR në mënyrë që të krijoja vonesa të bukura kohore. Artikujt që do t'ju nevojiten: 2x motorë stepper -htt

IOT123 - TRACKER SOLAR - TILT/PAN, PANEL FRAME, LDR MOUNTS RIG: 9 hapa (me fotografi)

IOT123 - Gjurmues SOLAR - TILT/PAN, KORNI PANEL, LDR MOUNTS RIG: Shumica e modeleve DIY për gjurmuesit diellorë me bosht të dyfishtë " atje " bazohen në 9G Micro Servo të cilat me të vërtetë janë të nënvlerësuara për të shtyrë rreth disa Qeli Diellorë, mikrokontrolluesin, baterinë dhe strehimin. Mund të dizajnoni rreth

Pan-Tilt Multi Servo Control: 11 hapa (me fotografi)

Pan-Tilt Multi Servo Control: Në këtë tutorial, ne do të eksplorojmë se si të kontrollojmë servos të shumtë duke përdorur Python në një Raspberry Pi. Qëllimi ynë do të jetë një mekanizëm PAN/TILT për të pozicionuar një aparat fotografik (një PiCam). Këtu mund të shihni se si do të funksionojë projekti ynë përfundimtar: Testi i lakut të kontrollit të servo Control:

Sintetizues Laser Harp në bordin Zybo: 10 hapa (me fotografi)

Sintetizues Laser Harp në Zybo Board: Në këtë tutorial ne do të krijojmë një harpë lazer plotësisht funksionale duke përdorur sensorë IR me një ndërfaqe serike që do t'i lejojë përdoruesit të ndryshojë akordimin dhe tonin e instrumentit. Kjo harpë do të jetë xhirim i shekullit 21 i instrumentit të vjetër.