Përmbajtje:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:15.

- E modifikuara e fundit 2025-01-23 15:10.

Lidhni bordin tuaj të zhvillimit Mojo me hyrje të jashtme me këtë mburojë.

Çfarë është bordi i zhvillimit Mojo?

Bordi i zhvillimit Mojo është një bord zhvillimi i bazuar në FPGA Xilinx spartan 3. Bordi është bërë nga Alchitry. FPGA janë shumë të dobishme kur procese të shumta duhet të ekzekutohen njëkohësisht.

Çfarë do t'ju duhet?

Furnizimet

Bordi i zhvillimit të Mojo

Dosja Gerber

Rezistenca 8 x 15k ohm (opsionale*)

4 rezistente 4 x 470 ohm

4 x 560 ohm rezistorë

4 x ekrane me shtatë segmente

4 x 3 mm LED

4 x çelsat prekës SPDT

Ndërprerës DIP i montimit në sipërfaqe 1 x 4

2 x 25 me 2 ose 4 x 25 tituj

Koka e kutisë 1x 2 me 5 pin

Makine per ngjitjen e metalit

Saldator

Fluksi

*(nëse këto rezistorë janë lënë jashtë tërheqja/tërheqja e brendshme duhet të jetë e aktivizuar për kunjat përkatëse)

Hapi 1: Ngarko Gerber tek Prodhuesi i Pcb sipas zgjedhjes suaj

Për bordet e mia kam porositur nga JLC PCB.

Ndryshimi i vetëm që bëra ishte ngjyra që doja të përputhej me të zezën e Mojo.

Hapi 2: Asambleja e Bordit

Kur bashkoj, gjithmonë më duket e dobishme të bashkoj pjesët më të ulëta së pari, kështu që fillimi me rezistorët është një ide e mirë.

R5, R6, R7, R8, R9, R10, R11 dhe R12 janë rezistenca 15k ohm të përdorura për të rrëzuar çelsat (nëse përdorni tërheqje/tërheqje të brendshme injoroni këtë).

R1, R2, R3, R4 janë rezistorë 560 ohm të cilët janë përgjegjës për kufizimin e rrymës përmes ekranit të segmentit 7.

R13, R14, R15, R16 janë rezistente 470 ohm të cilët janë përgjegjës për kufizimin e rrymës përmes 4 LED -ve.

Pastaj lidhni çelësin e zhytjes, çelsat prekës, LED -të, ekranet me shtatë segmente dhe lidhësin e kokës së kutisë në atë mënyrë.

Tani vendosni 25 me 2 (ose 2 25 me 1) në mojo për të rreshtuar kunjat. Drejtojeni mburojën me kunjat dhe ngjiteni në vend.

Hapi 3: Konfigurimi i softuerit

Për softuerin që i referohet faqes së internetit të Alchitry do t'ju njoftojë se çfarë ju nevojitet për të filluar dhe instaluar Xilinx ISE. Sidoqoftë, ndryshimi i skedarit.ucf në mënyrë që të dijë se cilat kunja janë të lidhura me atë që është e rëndësishme për të funksionuar programin tuaj.

Këtu është skedari.ucf që përdor me mburojën:

Konfiguro VCCAUX = 3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIUDHA "clk" 50 MHz LART 50 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; NET "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

Mos harroni nëse nuk i keni instaluar rezistencat për të redaktuar kunjat në.ucf me

| PULLDOWN; o

| TËRHEQ LART;

Nëse dëshironi të përdorni bllokun për ndonjë gjë, lidhjet janë si më poshtë. Majtas duke qenë numri i kunjit të bllokut dhe djathtas numri i pinit mojo që duhet të caktoni në.ucf tuaj:

pin 1 = 29

pin 2 = 51

pin 3 = 32

pin 4 = 41

pin 5 = 34

pin 6 = 35

pin 7 = 40

pin 8 = 33

pin 9 = GND

pin 10 = +V

Recommended:

Bordi i Zhvillimit DIY ESP32 - ESPer: 5 hapa (me fotografi)

Bordi i Zhvillimit DIY ESP32 - ESPer: Kështu kohët e fundit kam lexuar për shumë IoT (Internet of Things) dhe më besoni, thjesht mezi prisja të provoja një nga këto pajisje të mrekullueshme, me aftësinë për t'u lidhur me internetin, veten time dhe marr duart në punë. Fatmirësisht mundësia e një

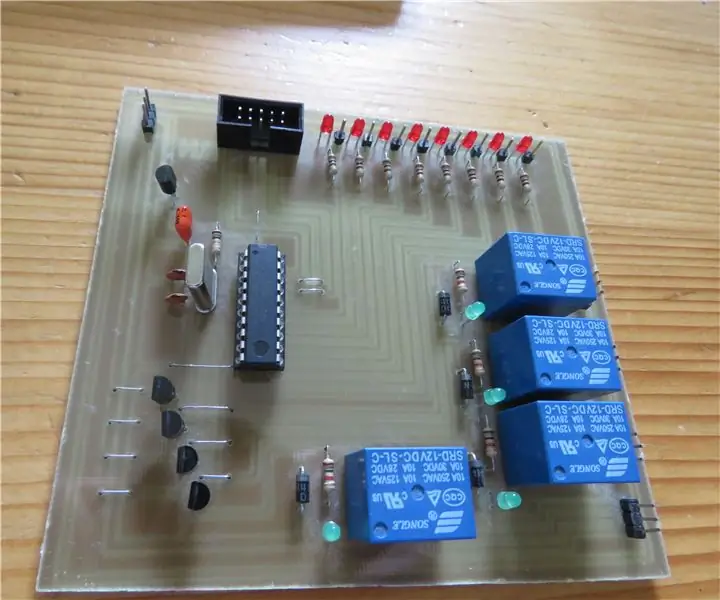

Krijoni bordin tuaj të zhvillimit me mikrokontrollues: 3 hapa (me fotografi)

Bëni Bordin tuaj Zhvillimor me Mikrokontrollues: A keni dashur ndonjëherë të bëni bordin tuaj të zhvillimit me mikrokontrollues dhe nuk e dini se si. Në këtë udhëzues unë do t'ju tregoj se si ta bëni atë. E tëra që ju nevojitet është njohuri në elektronikë, dizajnimin e qarqeve dhe programim. Nëse keni ndonjë kërkim

Luajtja e lojës Flappy Bird Me Bordin e Zhvillimit të M5stack Esp32 Bazuar në M5stick C: 5 Hapa

Luajtja e lojës Flappy Bird Me M5stack Esp32 Bazuar në Bordin e Zhvillimit M5stick C: Përshëndetje djema sot ne do të mësojmë se si të ngarkojmë kodin e lojës flappy bird në m5stick c bordin e zhvillimit të siguruar nga m5stack. Për këtë projekt të vogël do t'ju duhen dy gjëra: m5stick-c bordi i zhvillimit: https://www.utsource.net/itm/p/8663561.h

Bordi i Zhvillimit JALPIC One: 5 hapa (me fotografi)

Bordi i Zhvillimit JALPIC One: Nëse ndiqni projektet e mia Instructables ju e dini që unë jam një tifoz i madh i gjuhës programuese JAL në kombinim me Mikrokontrolluesin PIC. JAL është një gjuhë programimi si Pascal e zhvilluar për mikrokontrolluesit PIC 8-bit të Microchip. Mo

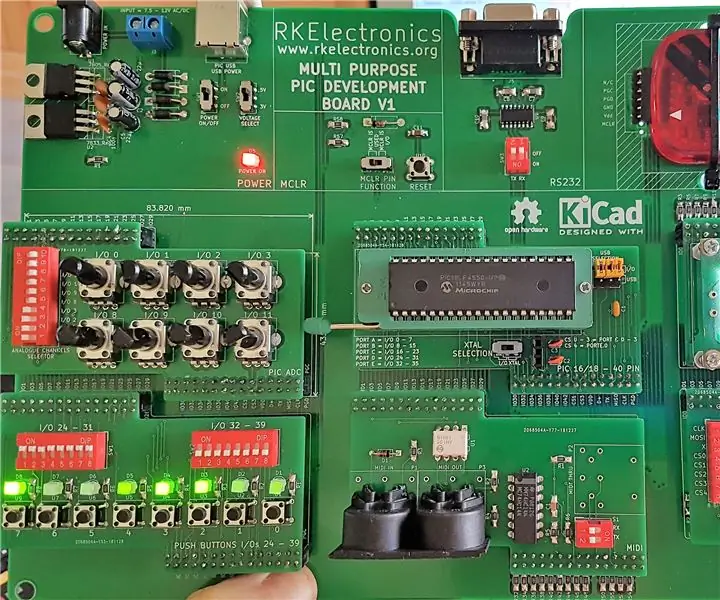

Sistemi i Bordit të Zhvillimit të Mikrokontrolluesve PIC: 3 hapa

Sistemi i Bordit të Zhvillimit të Mikrokontrolluesve PIC: Ky projekt është për hartimin dhe përdorimin e një mjeti të zhvillimit të PIC i cili është fleksibël për t'iu përshtatur një game të gjerë të projekteve elektronike të bazuara në PIC. Shpesh është më e lehtë të zhvillohen projekte të mikrokontrolluesve me përdorimin e mjeteve të zhvillimit; të cilat lejojnë përdoruesit të bazohen