Përmbajtje:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:10.

- E modifikuara e fundit 2025-01-23 15:10.

JDM është një programues i njohur PIC sepse përdor një port serik, një minimum të përbërësve dhe nuk kërkon furnizim me energji. Por ka një konfuzion atje, me shumë ndryshime programuesish në rrjet, cilat funksionojnë me cilat PIC? Në këtë "udhëzues" ne e vëmë JDM në provë dhe unë demonstroj se si të simulohet qarku duke përdorur Spice i cili do t'i përgjigjet të gjitha pyetjeve tuaja!

Furnizimet

LTspice e cila mund të shkarkohet nga Pajisjet Analog këtu.

Ju gjithashtu keni nevojë për skedarët e qarkut JDM këtu.

Hapi 1: Kërkesat e Portit Serial

JDM kërkon një port serik që plotëson specifikimet EIA232, në mënyrë ideale me nivele +12/-12 Tensioni.

Sipas fletës së të dhënave të Texas Instruments Line Driver MC1488 (Figura 3)

Impedanca e daljes = 4V/8mA = 500 ohm.

Kufiri i rrymës së qarkut të shkurtër = 12mV, pa kufi kohor - pa dëmtime të çipit.

Rezistenca e rezistencës hyrëse të marrësit të linjës = 3k deri në 7khm.

Portet serike në kompjuterët e vjetër desktop përdorin +12v/-12V që plotësojnë këtë kërkesë.

Portat serike në kompjuterët e rinj laptopë përdorin tensione më të ulëta. JDM mund ose nuk mund të funksionojë - përgjigja është më komplekse.

Hapi 2: Kërkesat e Programimit PIC

Informacioni në lidhje me kërkesat e programimit PIC merret nga Microchip. Sa më sipër është për një pajisje tipike.

Hapi 3: Specifikimi i JDM

A është humbur uebfaqja origjinale e JDM në mjegullat e kohës? Kjo na lë të hamendësojmë se çfarë synonte fillimisht projektuesi për specifikimin.

- Siguroni VDD = 5V, dhe deri në IDD = 2mA maksimale (për versionin "në prizë")

- Siguroni VHH = 13V, dhe deri në IHH = 0.2mA maksimum.

- MCLR Koha e ngritjes tVHHR = 1uS max.

- Versioni ICSP duhet të jetë në gjendje të tërheq MCLR të ulët kundrejt tërheqjes 22k në objektiv.

Hapi 4: Përshkrimi i qarkut

Figura JDM1 bazohet në qarkun "standard" JDM të marrë nga uebfaqja e PICPgm. Ky është programuesi "PIC in Socket" ku PIC merr energji nga kunjat TX dhe RTS. Diagrami origjinal ishte i vështirë për tu kuptuar, kështu që unë e rishikova duke përdorur konvencionin normal të rrjedhës së rrymës nga lart poshtë. Dhe unë kam shtuar treguesit LED "RESET", "PROG" dhe "RTS" të cilët janë të nevojshëm gjatë ndërtimit dhe testimit. Shpresojmë që këto të mos kenë ndonjë efekt të dëmshëm në sjellje.

Konventa normale e dizajnit të qarkut është e zakonshme në të gjitha bazat, por tipari kryesor i JDM është se toka serike e portit (GND) është e lidhur me VDD. Kjo krijon konfuzion pasi sinjalet serike të portit maten në lidhje me sinjalet GND, PIC në lidhje me tokën logjike (VSS).

Kur TX shkon lart, Q1 sillet si dy dioda të njëanshme përpara. (Kolektori i Q1 nuk është i njëanshëm i kundërt si me funksionimin normal të tranzistorit). Takuesi i T1 ngarkon C2, i cili mbërthehet në VDD+8V nga Zener (D3). Emetuesi i Q1 i jep 13V MCLR për modalitetin e programit/verifikimit.

Kur TX shkon poshtë, kondensatori C3 ngarkohet përmes D1 dhe VSS fiksohet në VDD-5V me zener (D5). Gjithashtu TX është kapur në (VSS-0.6) nga D1. Q1 është i fikur, C1 mban ngarkesën e tij për pulsin e ardhshëm të programimit. MCLR është fiksuar në 0V nga D2, kështu që PIC tani është Rivendosur.

Kur RTS është e lartë, ora transmetohet në PGC. Kapësja D4 PGC në logjikë VDD e lartë. Kur RTS është e ulët, kondensatori C3 ngarkohet përmes D6 dhe VSS fiksohet në VDD-5V me zener (D5). D6 mbërthen PGC në VSS ose logjikën 0.

Gjatë programimit, të dhënat e dërguara në DTR lexohen në PGD, të cilat PIC i konfiguron si hyrje. Kur DTR është e lartë, Q2 vepron si "përcjellës i emetuesit" dhe voltazhi i PGD është rreth (VDD-0.6) ose logjikë 1. Kur DTR është i ulët, Q2 vepron si një tranzistor i keq (kunjat e emetuesit dhe kolektorit të kundërt). Q2 tërheq PGD të ulët, e cila shtrëngohet nga D7 në VSS ose logjikën 0.

Gjatë verifikimit PIC konfiguron PGD si dalje për dërgimin e të dhënave në portën serike. DTR duhet të vendoset lartë dhe të dhënat lexohen në CTS. Kur dalja PGD është e lartë, Q2 është joaktiv, CTS = DTR = +12V. Kur prodhimi i PGD është i ulët, Q2 është i ndezur. Kolektori Q2 tërheq rrymën (12V+5V)/(1k+1k5) = 7mA nga DTR, dhe tërheq CTS ulët, në VSS.

Hapi 5: Përgatituni për Simulim

Shkarkoni erëzat LT, ruani dhe hapni skedarët e qarkut (*.asc) të dhënë këtu. Për të simuluar qarkun, duhet t'i japim disa hyrje, pastaj "gjurmojmë" daljet. V1, V2 V3 simulojnë portën serike 12V me rezistencë dalëse R11, R12, R13.

- V1 gjeneron 2 Pulsime Programi në TX nga 0.5ms në 4.5ms

- V2 gjeneron shpërthim të impulseve të të dhënave në DTR nga 1.5 në 4.5ms

- V3 gjeneron shpërthim të pulseve të orës në RTS nga 0.5 në 3.5ms

Komponentët V4, X1, R15 dhe R16 janë të gjithë pjesë e simulimit.

- V4 gjeneron 2 impulse nga 2.5 në 4.5ms për të verifikuar të dhënat.

- Jumper X1 simulon OUTPUT në PGD.

- R15, R16 simulojnë "ngarkimin" e PIC në VDD dhe MCLR.

Hapi 6: Ndryshimet për ICSP

Figura JDM3 tregon versionin për programimin "në qark". Ndryshimet nga origjinali janë

- Zëvendësoni prizën ZIF me lidhësin ICSP.

- PIC tani mundësohet nga qarku i furnizimit në objektivin (V5).

- Hiq zenerin 5V (D5).

- Kondensatori i vogël 100pF (C4) zhvendoset pranë PIC në qarkun e synuar.

- LEDs marrin energji nga bordi i qarkut aty ku është e mundur.

- Rezistenca tërheqëse MCLR (R10) dhe dioda (D10) kërkohen në qarkun e synuar.

- KUJDES Bordi i synuar duhet të ketë një furnizim "lundrues", në mënyrë ideale një bateri.

- Mos e lidhni tokën e synuar (VSS) me tokën e kompjuterit/PC -së duke lidhur ndonjë port tjetër kompjuterik në të njëjtën kohë me JDM.

Pas simulimit të JDM1, problemi i kohës së gjatë të ngarkimit në C2 u bë i dukshëm. Pastaj pas leximit të Fruttenboel duket se C2 dhe Q1 janë shtuar si modifikim në origjinal. Unë nuk mund të mendoj se çfarë synojnë të bëjnë C2 dhe Q1 përveç krijimit të problemeve. Pra, për JDM4, ne kthehemi në modelin më të vjetër në Fruttenboel i cili është i thjeshtë dhe i drejtpërdrejtë për tu kuptuar. D1 dhe D3/LED2 mbërthejnë MCLR midis VSS dhe VDD+8V. Vlera e R1 zvogëlohet në 3k3, mjafton të ndriçojë LED2 në 12V.

JDM4 është krijuar gjithashtu për të punuar me porte serike më të dobëta. Kur TX shkon lartë (+9V), burimi aktual i TX = (9-8)/(1k +3k3) = 0.2ma, aq sa për të tërhequr MCLR të lartë edhe pse i pamjaftueshëm për të ndriçuar LED2. Kur TX zbret (rreth -7V), lavamani i rrymës TX = (9-7)/1k = 2mA. Rryma LED1 = (7-2 për led)/(2k7) = 1.8mA. MCLR tërheq rrymën = 7-5.5/3k3 = 0.5mA.

Ky qark është testuar gjithashtu (simulimi JDM5) për të parë se çfarë ndodh me portet serike +/- 7V minimumi, ku ka tension të pamjaftueshëm për të mbajtur VHH = 13V. Qëllimi i C1 tani bëhet i dukshëm, C1 krijon një nxitje të shkurtër +ve në MCLR, një rritje 33us në skajin në rritje të TX, mjaftueshëm aq e gjatë sa që PIC të hyjë në modalitetin e programimit, ndoshta? Por hiqni kërcyesin X2 (çaktivizoni LED1) pasi nuk ka rrymë të mjaftueshme për të tërhequr MCLR të ulët dhe për të ndriçuar LED1 së bashku. Kur TX bie poshtë, lavamani i rrymës TX = (7V-5.5V)/(1k+3k3) = 0.3mA, vetëm sa për të tërhequr MCLR të ulët kundër R10 tërheqës.

Hapi 7: Rezultatet e simulimit

Për të parë skedarët grafikë, është më mirë të klikoni me të djathtën në lidhjet më poshtë, pastaj zgjidhni "Hap lidhjen në skedën e re"

Simulimi 1: gjurmë e MCLR, VSS dhe RTS për JDM1 origjinal. Vëzhgimet 1, 2 dhe 3 janë menjëherë të dukshme.

Simulimi 2: gjurmë e MCLR dhe VSS, dhe RTS për JDM2 të modifikuar, e cila rregullon problemet e mëparshme.

Simulimi 3: gjurmë e PGD, VSS dhe PGC për dërgimin e të dhënave JDM2 në modalitetin e programit. Vëzhgimi 4 në 3.5mS.

Simulimi 4: gjurmë e PGD, VSS dhe CTS për JDM2 në modalitetin e verifikimit (kërcyesi X1 i futur). Ne rregull

Simulimi 5: gjurmë e MCLR, VSS, PGD dhe PGC për JDM3. ICSP duke përdorur energjinë nga qarku zgjidh shumë probleme.

Simulimi 6: gjurmë e MCLR, VSS, PGD dhe PGC për JDM4 me port serial +/- 9V. MCLR ngrihet menjëherë, duke punuar plotësisht.

Simulimi 7: gjurma e MCLR, VSS dhe TX për JDM5 me portën seriale +/- 7V dhe kërcyesin X2 të hequr. C1 krijon një nxitje +ve (pik) në buzën në rritje të MCLR, pothuajse e mjaftueshme për të shtyrë MCLR mbi TX në 13V.

Hapi 8: Përfundime

Spice është vërtet i mirë në zbulimin e "sekreteve të fshehura" të funksionimit të qarkut. Me sa duket qarku JDM funksionon dhe është i pajtueshëm me shumë patate të skuqura PIC, por vëzhgimet e mëposhtme zbulojnë kufizime/probleme të pajtueshmërisë/gabimeve të mundshme?

- Koha e rritjes së gjatë të MCLR ndërsa C2 ngarkohet me VPP në pulsin e parë të TX. Dështon në specifikimet 3.

- Porti serik ngarkon C2 kur TX shkon lartë dhe RTS zbret poshtë. Por RTS gjithashtu ka detyrën e ngarkimit të C3. Kur të dy ndodhin në të njëjtën kohë kjo krijon më shumë ngarkesë në RTS, rrjedhimisht C3 humbet ngarkesën (VSS rritet) në 2ms në simulim. Dështon në specifikimet 1.

- C3 humbet ngarkesën (VSS fillon të rritet) pasi pulset e orës ndalojnë në 3.5ms.

- Cili është qëllimi i C2, është i nevojshëm fare?

Zgjidhjet

- Me sa duket PICPgm përdor një softuer "të rrumbullakët". Duhet të aplikojë një impuls të gjatë TX për të ngarkuar paraprakisht në C2, pastaj të hyjë në modalitetin e programimit vetëm pas pulsit të dytë TX? Për simulim, unë reduktova vlerën e C2 në 1uF për të dhënë një kohë ngritjeje prej 1ms. Jo një zgjidhje ideale.

- Ndani C2 dhe C3 në mënyrë që ata të ngarkojnë në mënyrë të pavarur. Një modifikim i vogël në JDM2, C2 i referohet GND në vend të VSS.

- E zgjidhur me JDM3. ICSP është shumë më e besueshme pasi PIC mundësohet nga qarku i synuar.

- JDM4 zgjidh problemin 1. Ky është një dizajn i drejtpërdrejtë që eliminon C2 fare.

Hapi 9: Dhe së fundi

Prova e pudingut është në të ngrënit. Ky JDM funksionon kështu që vazhdoni ta përdorni.

Dhe rekomandimet e mia janë:

- përdorni JDM2 për programimin e prizave dhe portet serike 12V,

- përdorni JDM4 për programuesin ICSP dhe portet serike mbi +/- 9V,

- përdorni JDM4 me bluzën X2 të hequr për portet serike mbi +/- 7V.

Referencat:

Pajisjet analoge erëza LT

figurë

Fruttenboel

Ndiqni më shumë projekte PIC në sly-corner

Recommended:

Rishikimi i kompjuterit Z80: 6 hapa

Rishikimi i kompjuterit Z80: Në të kaluarën, unë kam shkruar një udhëzues se si të ndërtoj një kompjuter të bazuar në Z80 dhe kam krijuar qarkun të jetë sa më i thjeshtuar që të jetë e mundur, në mënyrë që të ndërtohet sa më lehtë. Kam shkruar edhe një program të vogël duke përdorur të njëjtën ide të thjeshtësisë. T

Elegoo Super Started Kit Uno R3 Rishikimi: 4 hapa

Elegoo Super Started Kit Uno R3 Rishikimi: Disa ditë më parë Elegoo më dërgoni këtë Super Starter Kit për testim. Pra, le të shohim se çfarë ka brenda. Kur hapim këtë kuti kompakte ne mund të shohim shumë gjëra. Në kopertinë ka një indeks me të gjithë përbërësit. Brenda kemi një kartë falënderimi me të gjitha

Edhe një Mburojë tjetër e Programuesit ATP ATTINY85 për Arduino: 8 hapa

Edhe një Mburojë tjetër e Programuesit ATP ATTINY85 për Arduino: بسم الله الرحمن الرحيم Mburoja e Programuesit ATP ATTINY85 është projektuar për të programuar me lehtësi ATCMontrollers ATTiny85. Mburoja duhet të lidhet në tabelën Arduino Uno. Arduino Uno është e përgatitur të veprojë si një " Në qark Programues serial & quot

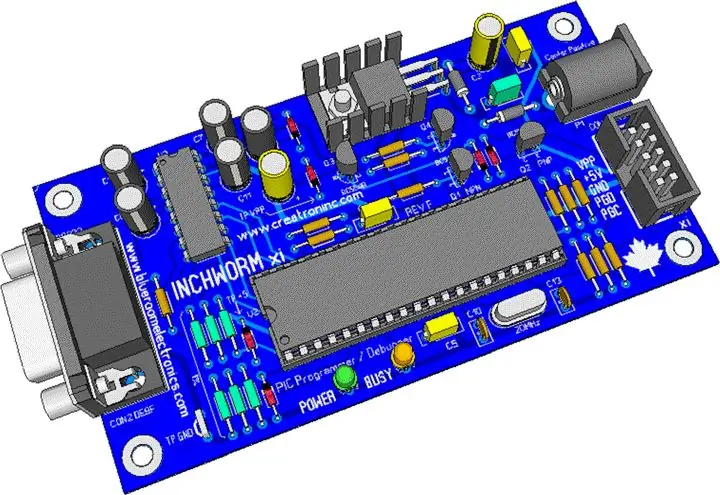

Ndërtimi i Programuesit PIC Inchworm ICD2 / Debugger: 7 hapa

Ndërtimi i Inchworm ICD2 PIC Programer / Debugger: Ky udhëzues është një shëtitje e ilustruar përmes ndërtimit të një kloni ICD2 të quajtur Inchworm.'Sshtë një çantë e drejtpërdrejtë që ju lejon të ndërtoni një Programues dhe Debugger të pajtueshëm me MPLAB ICD2. Ka shumë Programues atje, por shumë pak përfshijnë

Qëndrim për laptopë me 3 hapa dhe 3 hapa (me syze leximi dhe tabaka me stilolaps): 5 hapa

Qëndrim për laptopë me hapa 3 & 3 hapa (me syze leximi dhe tabaka për stilolapsa): Kjo $ 3 & Qëndrimi i laptopit me 3 hapa mund të bëhet brenda 5 minutave. It'sshtë shumë e fortë, me peshë të lehtë dhe mund të paloset për ta marrë kudo që të shkoni