Përmbajtje:

- Hapi 1: Bllokoni Diagramin

- Hapi 2: Parimi i funksionimit

- Hapi 3: Zbatimi i Logjikës

- Hapi 4: Zgjidhja e bllokimit

- Hapi 5: Konfigurimi i pajisjes - Qarku Matrix0

- Hapi 6: Konfigurimi i pajisjes - Logjika e Clocking SPI

- Hapi 7: Konfigurimi i pajisjes - Karakteristikat e komponentëve Matrix0

- Hapi 8: Konfigurimi i pajisjes - Qarku Matrix1

- Hapi 9: Konfigurimi i pajisjes - Numëruesi binar 3 -bit

- Hapi 10: Konfigurimi i pajisjes - Logjika e Krahasimit 3 -bitësh

- Hapi 11: Konfigurimi i pajisjes - Logjika e Krahasimit Dixhital dhe Regjistri i Përkohshëm

- Hapi 12: Konfigurimi i pajisjes - Karakteristikat e komponentëve të Matrix1

- Hapi 13: Rezultatet

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:13.

- E modifikuara e fundit 2025-01-23 15:10.

Sistemet e kontrollit dhe pajisjet e lidhura merren me burime të shumta energjie, të tilla si linja paragjykimi ose bateri, dhe duhet të gjurmojnë vijën më të lartë (ose më të ulët) midis një grupi të caktuar.

Për shembull, kalimi i ngarkesës në një sistem me shumë bateri kërkon që sistemi të monitorojë ose tensionin minimal ose maksimal midis grupit të baterisë (maksimum ose min si funksion i algoritmit të veçantë të kalimit) dhe të drejtojë në mënyrë dinamike ngarkesën në burimi më i përshtatshëm në kohë reale. Përndryshe, sistemit mund t'i duhet të shkëpusë përkohësisht baterinë e tensionit më të ulët për karikimin e duhur.

Një shembull tjetër është sistemi modern i energjisë diellore, ku çdo panel diellor është i pajisur me një mekanizëm tiltrotate dhe me një qark përcjellës diellor (ky i fundit siguron informacionin e pozicionit të Diellit për të orientuar panelin). Me informacionin e tensionit maksimal, çdo pozicion i panelit diellor mund të rregullohet mirë në bazë të panelit të vargut që në fakt jep tensionin më të lartë të daljes, duke arritur kështu një nivel superior të optimizimit të energjisë.

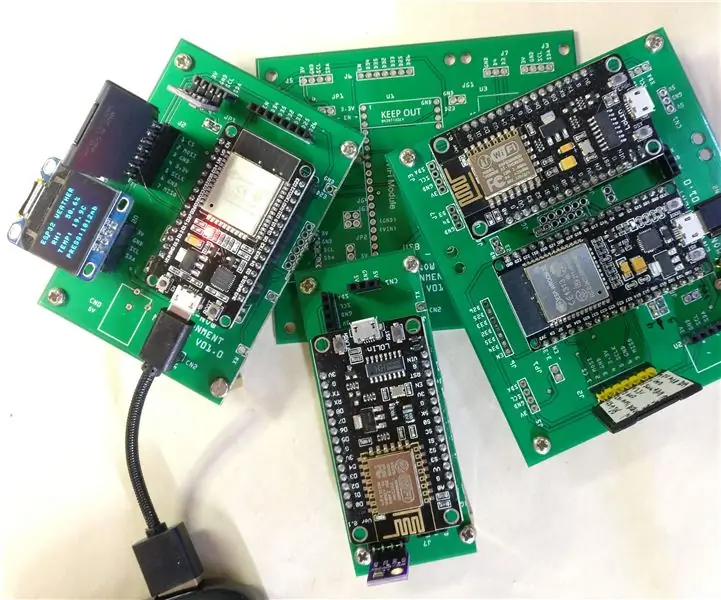

Ekzistojnë disa marka të ndryshme të IC -ve komerciale (kryesisht mikrokontrolluesit) që në parim mund të zbatojnë një përcjellës të tensionit maksimal. Sidoqoftë, ato kërkojnë programim dhe janë më pak kosto-efektive sesa një zgjidhje me sinjal të përzier. Plotësimi i një dizajni Dialog GreenPAKTM mund të ndikojë pozitivisht në përballueshmërinë, madhësinë dhe modularitetin e dizajnit. Ky dizajn shfrytëzon përfitimin e integrimit të qarkut analog dhe atij dixhital në një çip të vetëm.

Në këtë Udhëzues, pjesa e përparme analoge dhe logjika dixhitale e kërkuar për të zbatuar një gjetës të tensionit maksimal (ose përfundimisht min) midis tetë burimeve të ndryshme është zbatuar.

Për të zbatuar monitorin analog të tensionit maksimal/min me 8 kanale, përdoret një SLG46620G.

Më poshtë kemi përshkruar hapat e nevojshëm për të kuptuar se si është programuar zgjidhja për të krijuar monitorin analog të tensionit max-min me 8 kanale. Sidoqoftë, nëse thjesht doni të merrni rezultatin e programimit, shkarkoni softuerin GreenPAK për të parë Skedarin e Dizajnit të GreenPAK të përfunduar tashmë. Lidheni Kompletin e Zhvillimit GreenPAK me kompjuterin tuaj dhe goditni programin për të krijuar monitorin analog të tensionit maksimal/min me 8 kanale.

Hapi 1: Bllokoni Diagramin

Figura 1 tregon diagramin global të sistemit të zbatuar.

Një varg deri në 8 burime të tensionit të ndryshueshëm shumëfishohet dhe ndërlidhet me modulin ADC të GreenPAK të lidhur me një dizajn të brendshëm të personalizuar i aftë për të zgjedhur burimin me tensionin më të lartë në raport me të tjerët. Logjika e brendshme e nxjerr këtë informacion për shfaqje ose përpunim të mëtejshëm.

Dizajni bazohet në produktin GreenPAK SLG46620G, sepse ngërthen të gjitha blloqet e nevojshme analoge dhe dixhitale të ndërtimit për aplikimin. Në këtë zbatim, grupi skanohet me anë të një multiplexeri analog ADG508 të drejtuar drejtpërdrejt nga IC GreenPAK.

Informacioni dalës është një numër dixhital 3-bit që korrespondon me numrin e burimit të tensionit në tensionin maksimal. Një mënyrë e drejtpërdrejtë për të marrë këtë informacion është të tregoni numrin me anë të një ekrani me 7 segmente. Mund të arrihet lehtësisht duke bashkuar daljen dixhitale të SLG46620G me një drejtues të ekranit me 7 segmente, siç është zgjidhja GreenPAK e përshkruar në Referencë ose me një IC 74LS47 të përbashkët.

Qarku i paraqitur kërkon tension maksimal. Për ta shndërruar modelin në një zbulues të tensionit minimal, një qark i thjeshtë para-kondicionimi duhet të shtohet midis multiplexerit analog dhe hyrjes analoge të GreenPAK, duke zbritur daljen e multiplexerit nga një tension reference 1 V.

Hapi 2: Parimi i funksionimit

Dizajni synon të zgjedhë burimin me tension maksimal, prandaj një skanim kryhet në të gjithë grupin ndërsa ruan vlerën e fundit-max dhe e krahason atë me vlerën tjetër në hyrje (e cila i përket burimit tjetër të tensionit në skanim).

Në vijim do t'i referohemi një sekuence të plotë të multipleksimit përgjatë të gjitha hyrjeve si një "skanim" ose "lak".

Krahasimi midis dy vlerave nuk arrihet me anë të komponentëve ACMP (megjithatë, të disponueshëm në SLG46620G), por më tepër me modulin DCMP, pasi vlerat të digjitalizohen përkatësisht. Kjo është një teknikë e avancuar dhe e rafinuar e trajtuar së pari në Referencë.

Figura 2 tregon se si është strukturuar SLG46620G për këtë dizajn.

Sinjali analog i hyrjes shkon në hyrjen ADC përmes komponentit PGA me një Fitim të caktuar 1. Cilësime të ndryshme të Fitimit janë gjithashtu të mundshme për të gjetur ndeshjen më të mirë me elektronikën e kondicionimit të përparme të përkushtuar për të hartuar tensionet e hyrjes në 0-1 V gamën e modulit GreenPAK ADC.

ADC funksionon në modalitetin me një përfundim dhe konverton sinjalin analog në një kod dixhital 8-bit, i cili më pas transferohet në modulin DCMP. Kodi dixhital futet gjithashtu në bllokun SPI, i konfiguruar si një tampon ADC/FSM, ku një kod dixhital mund të ruhet dhe nuk do të ndryshojë derisa impulsi tjetër të vijë në hyrjen SPI CLK. Vini re se një bllok logjik i dedikuar drejton hyrjen SPI CLK. Ne do ta hetojmë këtë pjesë më vonë, pasi kjo është logjika "thelbësore" përgjegjëse për funksionimin e duhur. Një kod i ri dixhital ruhet në modulin SPI vetëm nëse i përket tensionit maksimal aktual të hyrjes.

Komponenti DCMP përdoret për të krahasuar të dhënat aktuale ADC me fituesin e fundit (që është maksimumi i fundit i gjetur) i cili ruhet në bllokun SPI. Do të gjenerojë një impuls në daljen OUT+ kur të dhënat e reja ADC janë më të mëdha se ato të mëparshme. Ne përdorim sinjalin OUT+ për të azhurnuar bllokun SPI me fituesin e ri.

Një sinjal global i orës drejton konvertimet ADC dhe oraret e përgjithshme. Pasi të bëhet një konvertim, sinjali i daljes INT i ADC -së pulson, i koordinuar në kohë me daljen paralele të të dhënave ADC. Ne përdorim daljen INT gjithashtu për të rritur një numërues binar 3-bit, të zbatuar nga DFF në Matrix1, i cili është i dobishëm për tre arsye:

1. Linjat dalëse të numëruesit i drejtohen multiplexerit analog të jashtëm, duke i shërbyer kështu tensionit të ardhshëm të hyrjes në ADC;

2. Numërimi ngrihet në një regjistër 3-bitësh (i zbatuar në Matrix1) për të ruajtur fituesin e përkohshëm gjatë një skanimi;

3. Numërimi deshifrohet për të përditësuar një regjistër të dytë 3-bitësh (të zbatuar në Matrix0) pasi të ketë përfunduar një skanim.

Hapi 3: Zbatimi i Logjikës

Moduli ADC siguron vazhdimisht të dhëna të konvertuara të të gjitha tensioneve hyrëse, njëra pas tjetrës, në mënyrë të pacaktuar. Pasi Multiplekseri të adresohet 0b111 (dhjetor 7), numëruesi rrotullohet në 0b000 (dhjetor 0) duke filluar kështu një skanim të ri të tensioneve të hyrjes.

Gjatë skanimit, sinjali dalës ADC INT gjenerohet kur dalja paralele e të dhënave është e vlefshme. Kur ky sinjal pulson, multiplexeri analog duhet të kalojë në hyrjen tjetër, duke i siguruar PGA tensionin përkatës. Prandaj, dalja ADC INT është sinjali i orës së drejtpërdrejtë të numëruesit binar 3-bit të figurës 2, fjala dalëse paralele 3-bit e të cilit i drejtohet drejtpërdrejt multiplexerit analog të jashtëm ("V select" në figurën 1).

Le t'i referohemi tani një shembulli ku tensionet e hyrjes supozohet të kenë marrëdhëniet e mëposhtme:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Figura 3 paraqet sinjalet kryesore të përfshira në mekanizmin e vendimit maksimal.

Meqenëse të dhënat përfundimisht futen në regjistrin tampon SPI në mënyrë sinkronike me pulsionet INT, ekziston një dritare krahasimi ku përmbajtja e tamponit SPI krahasohet me rezultatin tjetër të konvertimit ADC. Ky afat i caktuar rezulton në gjenerimin e impulseve OUT+ në daljen DCMP. Ne mund të përfitojmë nga këto impulse për të ngarkuar vlera të reja në regjistrin tampon SPI.

Siç duket nga linja e të dhënave tampon SPI e Figurës së mëparshme, regjistri SPI gjithmonë përmban, kohë pas kohe, vlerën më të madhe midis 8 hyrjeve dhe azhurnohet vetëm kur zbulohet një vlerë më e madhe nga moduli DCMP (referuar DCMP Linja dalëse OUT+ e komplotit, pulset e munguara bëjnë që V2 të mbetet i kyçur në regjistër derisa të krahasohet me V5).

Hapi 4: Zgjidhja e bllokimit

Nëse logjika e zbatuar do të ishte ashtu siç përshkruhet më sipër, është e qartë se ne do të përplasemi në një situatë bllokimi: sistemi është i aftë të zbulojë vetëm tensione më të larta se ai që korrespondon me atë që ruhet në regjistrin tampon SPI.

Kjo është gjithashtu e vlefshme në rast se ky tension do të ulet dhe pastaj një hyrje tjetër, deri tani më e ulët se ajo, bëhet më e larta: nuk do të zbulohej kurrë. Kjo situatë shpjegohet më mirë në Figurën 4 ku vetëm 3 tensione hyrëse janë të pranishme për hir të qartësi

Në kohën e përsëritjes 2, V3 bie dhe V1 është tensioni maksimal aktual. Por moduli DCMP nuk siguron një impuls sepse të dhënat e ruajtura në regjistrin tampon SPI (që korrespondon me 0.6 V) janë më të mëdha se ato që korrespondojnë me V1 (0.4 V).

Sistemi më pas sillet si një zbulues maksimal "absolut" dhe nuk azhurnon daljen në mënyrë korrekte.

Një mënyrë e mirë për të kapërcyer këtë problem është që të ngarkoni me forcë të dhënat në Regjistrin Buffer të SPI kur sistemi të përfundojë një cikël të plotë të votimit të të gjitha kanaleve.

Në fakt, nëse voltazhi në atë hyrje është akoma më i larti, asgjë nuk ndryshon dhe kontrolli vazhdon në mënyrë të sigurt (referuar Figurës 4 më lart, ky është rasti i Përsëritjeve të Lakit 0 dhe 1). Nga ana tjetër, nëse voltazhi në atë hyrje ulet rastësisht në një vlerë më të vogël se një hyrje tjetër, atëherë rimbushja e vlerës i jep mundësinë modulit DCMP të prodhojë një impuls OUT+ kur e krahasojmë me vlerën e re maksimale (kjo është rasti i përsëritjeve të ciklit 2 dhe 3).

Një pjesë e qarkut logjik është e nevojshme për të kapërcyer problemin. Duhet të gjenerojë një sinjal sahati në komponentin SPI kur laku të arrijë hyrjen maksimale aktuale, duke detyruar kështu një ri-ngarkim të fjalës së tij të përditësuar të të dhënave në Regjistrin Buffer SPI. Kjo do të diskutohet në Seksionet 7.2 dhe 7.6 më poshtë.

Hapi 5: Konfigurimi i pajisjes - Qarku Matrix0

SLG46620G ka dy blloqe matricash, siç përshkruhet në figurën 2. Figurat e mëposhtme tregojnë konfigurimet përkatëse të pajisjes.

Pjesa e sipërme e qarkut është "Regjistri i Loop" i realizuar me 3 DFF (DFF0, DFF1 dhe DFF2). Refshtë rifreskuar pas çdo lak të multiplexer-it hyrës për t'i dërguar një drejtuesi të ekranit me 7 segmente numrin binar të "fituesit", që është hyrja me tensionin më të lartë në skanimin e fundit. Si ora në DFF ashtu edhe të dhënat vijnë nga logjika e zbatuar në Matrix1 përmes, përkatësisht, portit P12, P13, P14 dhe P15.

Pjesa e poshtme është pjesa e përparme analoge me hyrje në Pin 8 dhe PGA me fitim x1. Dalja ADC INT shkon si në logjikën e kohëzgjatjes së SPI ashtu edhe në Matrix1 përmes portës P0, ku do të shërbejë si sinjal i orës për numëruesin e zbatuar.

Daljet paraprake të të dhënave ADC dhe SPI etiketohen përkatësisht NET11 dhe NET15 për t'u lidhur me komponentin DCMP në Matrix1.

Hapi 6: Konfigurimi i pajisjes - Logjika e Clocking SPI

Siç u theksua më parë në seksionin "Zbatimi i Logjikës", Regjistri i Buferit SPI azhurnohet çdo herë që një krahasim midis vlerës aktuale të ruajtur dhe të dhënave të reja të konvertimit ADC gjeneron një impuls në daljen DCMP OUT+.

Integriteti i sinjalit sigurohet nëse ky sinjal është AND-ed me daljen ADC INT. Kjo shmang çdo nxitje dhe nxitje të rreme.

Ne gjithashtu kemi nënvizuar se për të anashkaluar situatat e bllokimit, SPI Buffer duhet të përditësohet kur cikli arrin të dhënat aktuale të fituesit.

Tre sinjale atëherë janë në lojë për përcaktimin e duhur të SPI:

1. Dalja ADC INT (LUT0-IN1)

2. DCMP OUT+ dalje (LUT0-IN0 përmes portës P10)

3. Numërimi është i barabartë me sinjalin Latch (LUT0-IN2 përmes portës P11)

Dy të parat janë AND-ed dhe të dy OR-ed me këtë të fundit në LUT0, zbatimi i të cilit është i konfiguruar si në Figurën 6.

Hapi 7: Konfigurimi i pajisjes - Karakteristikat e komponentëve Matrix0

Figurat 7-10 tregojnë komponentët e mbetur të dritareve të pronësisë që i përkasin Matrix0.

Hapi 8: Konfigurimi i pajisjes - Qarku Matrix1

Hapi 9: Konfigurimi i pajisjes - Numëruesi binar 3 -bit

Pjesa e sipërme e qarkut përmban elemente logjike, kryesisht një numërues binar 3-bit të rregulluar nga dalja ADC INT, siç është diskutuar tashmë. Ky sportel është zbatuar me një skemë mjaft "standarde" të treguar në Figurën 12.

Ky sportel është realizuar në dizajnin tonë me anë të Flip-Flops DFF9, DFF10, DFF11 dhe INV1, LUT4, LUT8. Dalja DFF9 është LSB ndërsa DFF11 është MSB siç tregohet në Figurën 13.

LUT4 është konfiguruar si XOR ndërsa LUT8 kryen logjikën AND-XOR të Figurës 12.

Numëruesit dalin në tre kunja dalëse dixhitale për të adresuar Multiplekserin Analog të jashtëm.

LUT10 deshifron kodin e numëruesit kur skanimi është i plotë dhe ushqen një impuls në Matrix0 përmes DLY8 dhe portës P12. Kjo thjesht arrihet duke AND-ing daljet e numëruesit, duke deshifruar kështu numrin 7 dec (0b111 binar, fundi i lakut).

Hapi 10: Konfigurimi i pajisjes - Logjika e Krahasimit 3 -bitësh

Figura 15 tregon qarkun e përdorur për të zbuluar kur laku po përsëritet në adresën aktuale "fituese". Në këtë rast, siç u diskutua tashmë, një impuls dixhital duhet të detyrojë një rimbushje të rezultatit aktual ADC për të zgjidhur një situatë të mundshme bllokimi.

Adresa "fituese" ruhet në regjistrin e përkohshëm të Matrix1 (shiko më poshtë), ndërsa adresa aktuale prodhohet nga numëruesi binar.

Portat XNOR sigurojnë një dalje të vërtetë (logjike 1 ose "e lartë") kur të dy hyrjet janë të barabarta. AND-ing ky sinjal për të gjitha bitët (LUT9) na jep një impuls kur të dy kodet binarë janë të njëjtë. Detajet rreth portave XOR si kontrollues i barazisë mund të gjenden në Reference.

Sinjali "Counter-equals-Latch" kalohet në Matrix0 përmes portës P11.

Hapi 11: Konfigurimi i pajisjes - Logjika e Krahasimit Dixhital dhe Regjistri i Përkohshëm

Pjesa e poshtme e figurës 11 (e theksuar në figurën 16) tregon bllokun DCMP, pjesa vendimmarrëse e këtij dizajni.

DFF6, 7 dhe 8 formojnë një regjistër 3-bit për të ruajtur numrin e përkohshëm të hyrjes "fitues" ndërsa laku është duke funksionuar. Hyrjet në Flip-Flops janë daljet binare 3-bitëshe të numëratorit, siç shihen në qarkun global Matrix1 të Figurës 11, të kaluara këtu për hir të qartësisë.

Rezultatet e këtij regjistri nuk mund të drejtojnë drejtpërdrejt ekranin me 7 segmente sepse vlera e ruajtur këtu ndryshon gjatë një skanimi dhe duhet të konsiderohet "e vlefshme" vetëm në fund të vetë skanimit.

Për këtë arsye, daljet e regjistrit të përkohshëm lidhen me Regjistrin e Matjeve të Matrix0 përmes portave ndër-matricë P13, P14 dhe P15.

Figureshtë e rëndësishme të vërehet në Figurën 16 që regjistri i përkohshëm të përcaktohet nga dalja DCMP OUT+ kur ADC-SPI regjistron rezultatet e krahasimit në një maksimum të ri të gjetur.

I njëjti sinjal OUT+ i kalohet Matrix0, SPI CLK Logic, nëpërmjet portës P10.

Hapi 12: Konfigurimi i pajisjes - Karakteristikat e komponentëve të Matrix1

Figurat 17-19 tregojnë dritaret e pronës përbërëse që i përkasin Matrix1.

Hapi 13: Rezultatet

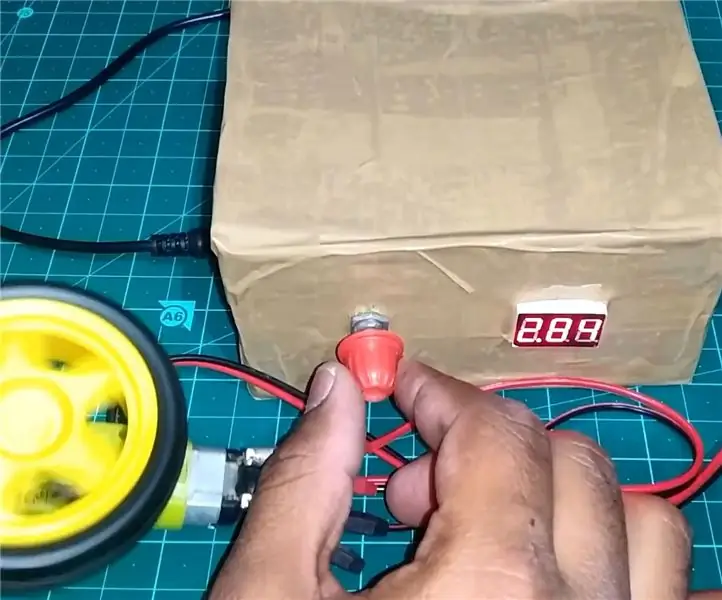

Për të testuar zbatimin, është krijuar një prototip i bordit të vlerësimit, ku 8 tensionet analoge të hyrjes merren nga një seri ndarësish të rezistencës me TrimPots (siç tregohet në Figurën 20).

Multiplekseri i përdorur është një ADG508, një pjesë që mund të funksionojë me një furnizim të vetëm (12 V).

Drejtuesi i ekranit me 7 segmente është një 74LS47. Ai dekodon një fjalë hyrëse paralele dhe drejton drejtpërdrejt një ekran me segment të përbashkët 7-segmentesh.

Bordi i vlerësimit ka një lidhës me kënd të drejtë 2x10 për t'u lidhur direkt me një Platformë të Zhvillimit të Avancuar GreenPAK në lidhësin e tij të zgjerimit siç tregohet në Figurën 21.

Lidhja me Platformën e Zhvillimit të Avancuar GreenPAK e bën shumë të thjeshtë marrjen e matjeve të sinjaleve për një kontroll të shpejtë. Për shembull, Figura 22 tregon një sërë sinjalesh (përkatësisht ORA, dalja ADC INT dhe dalja DCMP OUT+) të kapura nga një Analizues Logjik HP 54620A. Format e valëve nxiten nga një buzë në rritje e sinjalit OUT+ (në fushën e etiketuar si 'A> B'), prandaj kjo është një kapje e formës së valës kur një Tension i ri maksimal zbulohet midis hyrjeve analoge. Në fakt, është marrë duke rrotulluar njërën nga TrimPots të Bordit të Vlerësimit për të rritur tensionin përkatës të treguar në Figurën 22.

Figura 23 tregon skemën e Bordit të Vlerësimit.

Përfundim

Në këtë Instructable, ne zbatuam një gjetës të tensionit maksimal me tetë kanale (ose min) për t'u përdorur si një shtesë e zakonshme në sistemet e kontrollit me shumë kanale. Qasja e paraqitur shfrytëzon veçoritë e përparuara të komponentëve të GreenPAK dhe tregon se si është e mundur të integrohen në një funksion të vetëm analog dhe dixhital të një çipi. Disa IC të tregtisë mund të zëvendësohen me Dialog GreenPAK në mënyrë që madhësia dhe kostoja e aplikimit të zvogëlohen.

Recommended:

Madhësia e xhepit DIY Matës i tensionit DC: 5 hapa

Matës i tensionit DC i madhësisë së xhepit DIY: Në këtë udhëzues unë do t'ju tregoj se si të bëni matës tensioni DC me madhësi xhepi DIY me zile piezo për kontroll qarku vetë. E tëra që ju nevojitet është njohuri bazë në elektronikë dhe pak kohë. Nëse keni ndonjë pyetje ose problem, mund të

Monitorues i tensionit për bateri me tension të lartë: 3 hapa (me fotografi)

Monitori i Tensionit për Bateritë e Tensionit të Lartë: Në këtë udhëzues do t'ju shpjegoj se si kam ndërtuar monitorin e tensionit të baterisë për dërrasën time elektrike. Montojeni si të doni dhe lidhni vetëm dy tela me baterinë tuaj (Gnd dhe Vcc). Ky udhëzues supozoi se tensioni i baterisë tuaj tejkalon 30 volt, w

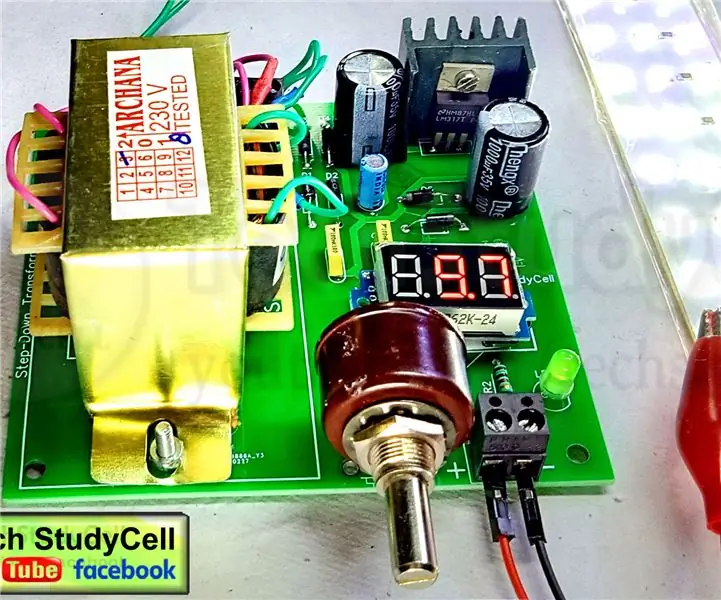

Furnizimi me energji DIY duke përdorur LM317 - Lm 317 Prodhimi i Tensionit të Ndryshëm: 12 Hapa

Furnizimi me energji DIY duke përdorur LM317 | Lm 317 Prodhimi i Tensionit të Ndryshëm: Sot do të mësojmë se si të bëjmë një njësi të vogël të furnizimit me energji për projektet tuaja të vogla. LM317 do të jetë zgjidhja e mirë për furnizimin me energji të ulët aktuale. Lm317 siguron tension të ndryshueshëm dalës i cili varet nga vlera e rezistencës që është e lidhur në të vërtetë wi

Furnizimi me energji DC i Tensionit të Rregullueshëm Duke përdorur Rregullatorin e Tensionit LM317: 10 Hapa

Furnizimi me Rrymë i Tensionit i Rregullueshëm Duke Përdorur Rregullatorin e Tensionit LM317: Në këtë projekt, unë kam hartuar një furnizim të thjeshtë me tension të rregullueshëm DC duke përdorur IC LM317 me një diagram qarkor të furnizimit me energji LM317. Meqenëse ky qark ka një ndreqës të integruar të urës, kështu që ne mund të lidhim drejtpërdrejt furnizimin AC 220V/110V në hyrje.

Përfitimi maksimal nga porosia juaj e PCB (dhe rregullimi i gabimeve): 4 hapa

Përfitimi maksimal nga porosia juaj e PCB (dhe rregullimi i gabimeve): Kur porositni PCB në internet, ju shpesh merrni 5 ose më shumë nga PCB identike dhe jo gjithmonë keni nevojë për të gjitha ato. Kostoja e ulët e marrjes së këtyre PCB-ve me porosi është shumë tërheqëse dhe ne shpesh nuk shqetësohemi se çfarë të bëjmë me ato shtesë. Ne nje